主题中讨论的其他器件:、 UCC2895

您好!

在轻负载下、在突发模式期间每隔几次就可以看到图1中的波形。

这是怎么回事?

我通常大多数时候都使用图2。

这是否正常? 是否有任何对策?

我正在致力于提高轻负载的效率。

我想如果把它删除、效果会更好。

此致

e2e.ti.com/.../Wave-form_5F00_Light-Load.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在轻负载下、在突发模式期间每隔几次就可以看到图1中的波形。

这是怎么回事?

我通常大多数时候都使用图2。

这是否正常? 是否有任何对策?

我正在致力于提高轻负载的效率。

我想如果把它删除、效果会更好。

此致

e2e.ti.com/.../Wave-form_5F00_Light-Load.pdf

您好!

请注意、两个 波形在变压器上都有过度的振铃、这种情况是不应该存在的。 您可能希望找出导致此振铃的原因并从设计中消除。 这可能是由布局/原理图错误导致的。

在图1中、您正确地看到变压器两端的极性应每隔一个周期改变一次、包括突发模式。 因此您不会看到这种行为。

有些采用 UCC28950、UCC28950EVM-442的600W 参考设计可能需要订购和评估。 通过以下链接可访问此评估模块的用户指南。 本用户指南中包含您可能希望评估的原理图、布局和测试数据。 https://www.ti.com/lit/ug/sluu421a/sluu421a.pdf

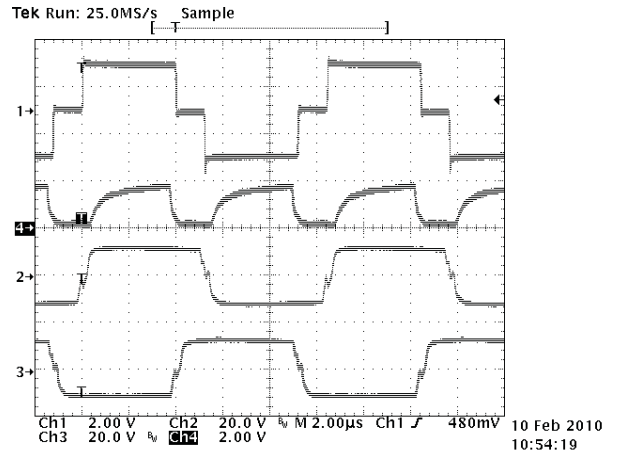

以下波形取自600 W UCC28950评估模块。 CH1是变压器和匀场电感器两端的电压。 CH4是 CS 信号、CH2和 CH3是低侧 FET 栅极。 从这些波 形中可以看到波形中没有过多的振铃。

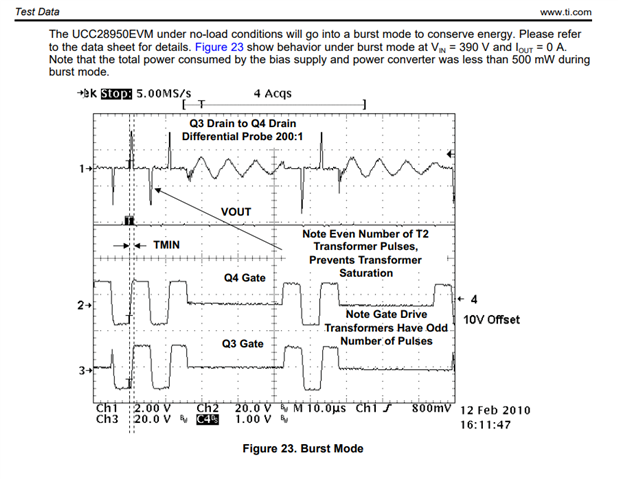

用户指南中介绍了突发模式下的行为。 图23下面的是您在突发模式下应该观察到的行为。 变压器两端的电压应每隔一个周期改变一次极性。

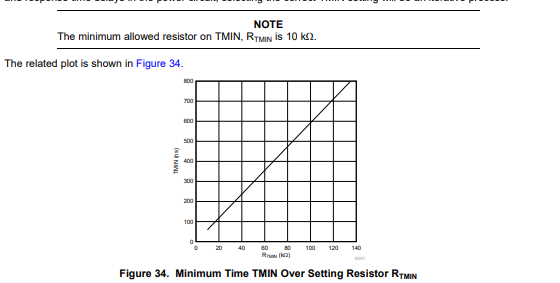

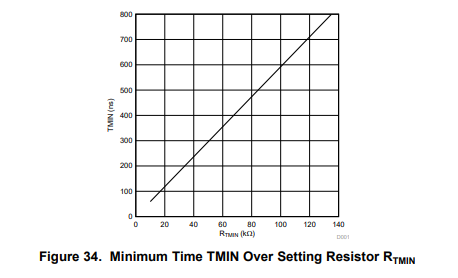

在轻负载突发中观察波形时、您的最小占空比设置为40%。 此电平过高、可能会导致一些问题。 UCC28950的引脚 Tmin 设置突发前的最小占空比。 您可能需要将 RTmin 设置为10k Ω、以查看问题是否得到解决。 这将在突发前提供50ns*(开关频率)的最小占空比。

以下链接可为您提供一份应用手册、其中介绍了使用 UCC28950 PSFB 控制器的移相全桥的分步设计过程。 应用手册中甚至 提供了一个链接、指向使用与应用手册中所示公式相同的 Excel 设计工具。 您可以同时使用应用手册和 Excel 设计工具进行设计、以检查您的设计。

https://www.ti.com/lit/pdf/slua560

此致、

你好

有一个很好的解释。

该电源是可变电源。

最大值为120V。

这次的波形是输出为50V/0.1A 时的波形。

我觉得由于关断周期长、次级侧 L 的能量消失了、出现了谐振。

考虑到以上情况、还是很不正常?

我开始感到焦虑。

此外、匀场电感器设置为10uH。

如果匀场电感器太大、是否会发生类似这样的振铃?

在 Excel 设计工具中、从1到4 μH。

使用 Excel 设计工具。

然而、由于输出范围很宽、很难判断其是否正确。

RTMIN 值为15kΩ。

不过、导通宽度约为1.44usec。

即使降低电阻值、它也不会变得更短。

这是什么原因造成的?

我检查了 UCC28950的栅极信号。

在前面讨论的波形中、延迟的 MOSFET (OUTD)似乎先关断。

附加的栅极信号会有延迟、因为前面有驱动器 IC 和驱动变压器。 我们将给您发送电路图。

如果您找出原因、请告诉我。

您好!

您可能直接涉及电感器谐振、因为电感器为 gong dcm。 您可以通过研究电感器电流与为验证此情况而采用的波形来验证这一点。

匀场电感器将与变压器初级磁化电感器形成一个分压器。 只要该值不会过大、就不会产生问题。 我认为、如果与 Lm 相比、它是10%或更低、那么不会产生问题。

如果将 RTmin 设置为15k 欧姆、则施加的变压器最小电压应为75ns。 即使控制器已突发,也可能不是由 tmin 引脚控制的轻负载突发造成的。

您可能需要研究 COMP、CS、SS 以及变压器和 Shim 电感器上的电压。 这可能会让您知道设计为什么令人兴奋。

我查看了随附的原理图、其中包括功率级、H 桥驱动器和电流检测变压器以及输出整流器。 不存在控制器部分和输出滤波器。 我看到、输出整流器上有缓冲器、可用于抑制您在变压器初级侧观察到的直流振铃。 这也可能对 EMI 有所帮助。

我还注意到、您在匀场电感器和变压器的初级侧之间使用了钳位二极管。 很多工程师错过了这个、因此他们需要保护次级整流器免受过压影响。

此致、

你好

昨天发送的波形中存在错误。

OUTD 首先开启、然后开启 OUTA。

只要 OUTC 和 OUTD 提前、运行似乎没有区别。

在目录中、OUTA 和 B 正在进步。

这种行为是否正常?

如果出现异常、原因是什么?

此外、当我再次获取波形时、可以进行占空比控制。

我很担心、因为我没有任何改变。

哪一个常数对回顾驱动有效?

但是我觉得如果进一步降低占空比、轻载时的损耗会增加。

如果是、那么将 TMIN 设置为1usec 是否存在问题? (RTMIN:100K~200kΩ)

此外、振铃是由次级侧的 L 导致的。

我们还将为您发送控制部分的电路。

此致

您好!

在第一个波形中、有 B、C 和变压器输入电压。 该波形不会同时显示与变压器上的电压相对应的 B 和 C ON。 您确定这是该波形中的 OUT B 和 OUT C 吗? 如果是、您的 H 桥中连接了错误的东西。

第二个波形具有 A、OUT C 和变压器电压。 在变压器上施加电压时不会显示此情况。 您必须注意 A、D 和变压器输入电压。

变压器两端的电压应与 A 和 D 输出以及 B 和 D 输出保持一致。 当 A 和 D 同时导通时、将会在变压器上施加电压。 当 B 和 C 同时导通时、将在变压器上反向施加电压。

该行为通常而言、变压器两端的电压将交替变化。 在您在显示的波形中、在负方向上似乎有一个小占空比。 在正常占空比再次为负后不久发生。 将 变压器以相同方向 连续两个周期施加电压是不正常的现象。

我向您推荐的是以下内容。

1. 仔细检查所测得的波形、确保占空比正确并与相应的输出对齐。

2. 仔细检查原理图,确保 H 桥连接正确。

此致、

你好

抱歉

第二个波形是 A 和 D OUT 信号。

由于这两个输出都是 IC 的输出、因此由于后续驱动 IC 和驱动变压器的影响、它们不会与变压器上的电压同步。

另外、您说不能同时看到、但箭头所示的部分同时打开。

正如第一个人指出的、我听说在两个连续周期内按相同方向向变压器施加电压是不正常的。

当时,我收到的意见是,原因可能是 TMIN 没有收窄。

前一份报告指出、发现 IC 输出的占空比有所降低。

因此、我想问一个问题、驱动变压器和驱动 IC 的外围常数中应查看哪些常数。

我检查了电路和图案、发现没有问题。

您发送的电路是否有任何问题?

另外,请回答我前几天提出的问题。

"我①的理解是、首先打开 OUT_A、B 还是 OUT_C、D 都无关紧要吗?

(就 IC 运行而言、一个打开是否大于 D?)

②我将 TMIN 设置为1usec 有什么问题吗? (RTMIN:100k 至200kΩ)

此致

你好

您看了变压器两端的电压、表示导通宽度没有缩小。

但是、如果负载较轻、能量会留在变压器的次级侧、因此可能无法根据变压器两端的电压确定实际宽度。

负载系数约为1%。

另外,请回答我前几天提出的问题。

①我将 TMIN 设置为1usec 有什么问题吗? (RTMIN:100k 至200kΩ)

②I 想抑制这种反向感应分量、但在栅极和源极之间放置一个 SBD 是否可以?

如果你有任何其他措施,请告诉我。

此致

您好!

如果两个相位都不是续流的、则变压器两端的电压将处于导通时间。 如果您想根据 UCC28950控制器确定确切的导通时间、则必须查看.. 输出 D 。当输出 A 和输出 D 同时导通时、这将是 UCC28950的导通时间。 当输出 B 和输出 C ON 同时导通时、这将是 UCC28950的导通时间。

1.关于设置最小 TMIN、我建议仅使用10k 至135k 欧姆之间的电阻器。 这就是 TMIN 的表征位置。

2.有一个 DCM 引脚可用于在电流中断之前关闭 FET。 这可以通过 Vref 和 DCM 引脚之间的电阻分压器进行设置。 如果 CS 引脚上的峰值电流不超过 DCM 阈值、则将禁用 SR FET。 数据表中的第7.3.12节介绍了如何设置该 DCM 比较器。

此致、

你好

感谢您的回答。

我的电源在次级侧进行二极管整流。

我是否理解了降低 DCM 值会将负载从轻负载变为 CCM 模式?

我目前遇到了在从 DCM 模式切换到 CCM 模式的负载区域 MOSFET 产生热量的问题。

关于宽输出电压范围

在以下情况下、是否应将 DCM 设置为最低电压?

最小电压(最小功率) 30V/10A

最大电压(最大功率) 100V/12A

我还有一个问题。

当它由驱动变压器驱动时也是如此。

如果在 MOSFET 的栅极和源极之间添加肖特基势垒二极管、是否存在问题?

(方向:栅极侧的阳极)

此致

您好!

请在下方查看我对您问题的答复。

我的电源在次级侧进行二极管整流。

我是否理解了降低 DCM 值会将负载从轻负载变为 CCM 模式?

>当 Iout -(Change Iout/2)为0或更小时、该设计将进入 DCM 模式。 避免-电感器中的电流会导致 SR FET 损坏。

>建议在 Iout 为0A 之前使用 DCM 引脚关断 FET -(Change ILout/2)。

我目前遇到了在从 DCM 模式切换到 CCM 模式的负载区域 MOSFET 产生热量的问题。

关于宽输出电压范围

在以下情况下、是否应将 DCM 设置为最低电压?

>在 Iout 之前将该负载的10%到15%-(更改 ILOUT/2)= 0A。

最小电压(最小功率) 30V/10A

最大电压(最大功率) 100V/12A

我还有一个问题。

当它由驱动变压器驱动时也是如此。

如果在 MOSFET 的栅极和源极之间添加肖特基势垒二极管、是否存在问题?

(方向:栅极侧的阳极)

>如果您这样做,将无法关闭二极管。

>以下链接将带您进入采用 UCC28950闸极驱动变压器的600 W 参考设计。 您可以将其用作在此应用中应如何使用栅极驱动器变压器的参考。

https://www.ti.com/lit/pdf/sluu421

此致、

您好!

如果未使用 SR、并希望保持设计在 CCM 模式、则只需增加电感器的尺寸即可增加电感器纹波电流。

如果根据 Iout*0.2选择电感纹波,设计将在10%负载时进入临界传导。 这会使设计在 CCM 下工作至10%负载。 这符合您15%的裕度要求。

UCC2895仅控制峰值电流、而不控制通过电感器 dI 的纹波电流。 电感器纹波电流(dI)基于施加在电感器上的电压(V)、施加在电感器和电感器(L)本身上的时间(dt)。 您可以使用以下公式帮助确定 dI

V*dT/L = dI

此致、

你好

有一天,你告诉我:

"如果您未使用 SR、并希望使设计保持在 CCM 模式、则只需增加电感器的尺寸即可增加电感器纹波电流。"

增加尺寸意味着什么?

如果 L 值降低、DI 是否不会增加?

我购买的产品 L 值增加、我是否需要进行实验?

另请回答我昨天提出的问题。

顺便说一下、即使我不使用 SR、我是否可以通过短接 DCM 端子和 GND 来强制它进入 CCM 模式?

或者、除非使用 SR、否则 DCM 端子是否没有意义?

此致

>您好,

请在下方查看我的回答。

>增加规模意味着什么?

>如果您没有使用 SR,设计仍可进入 DCM。

> Iout -更改 ILout/2是设计进入 DCM 的位置。

> ILout 变化= (Vout +Vd)*(1-D)*(1/FSW)*(1/LOUT)

>增大 Lout 将减小 ILout 的变化。 它将使设计能够长时间保持在 CCM 下。

如果 L 值降低、DI 是否不会增加?

>是的,这会导致您的设计更快进入 DCM。

另请回答我昨天提出的问题。

顺便说一下、即使我不使用 SR、我是否可以通过短接 DCM 端子和 GND 来强制它进入 CCM 模式?

> DCM 引脚不会强制设计进入 DCM。 它用于在使用 SR 时阻止 FET 在其中获得反向电流。

>如果您使用 SR,此引脚将在设计进入 DCM 之前禁用 SR 驱动器。

或者、除非使用 SR、否则 DCM 端子是否没有意义?

>DCM 引脚不会强制使设计停止工作 ,它用于保护 FET。

此致、

你好

感谢您的联系。

我会思考一下。

其他问题。

如果输出电压范围较宽、则表明在所有方面都很难实现 ZVS。

目前、当输出为低电平时、将负载施加到10%到40%时会有很大的损耗。

QA 和 QB 尤其热。

作为对策、增大垫片电感的 L 值将产生良好的效果。

但是、随着 LS 值的增加、FR 也会增加、因此计算出的 TABSET 和 TCDSET 值也会增加。 请告诉我将 DelayTime 设置为小于此处计算的时间的缺点。

目前、我想将计算值从170ns 更改为70ns。

请再说一件事。

这可能是上述缺点之一。

随着 LS 值的增加、高输出区域的输出电压会显著下降。 除了降低 LS 值之外、是否有其他对策?

此致

您好!

您需要根据最坏情况设置 Ls、以帮助在所有情况下实现 ZVS。 在本例中、我会在较高的输出电压下选择 Ls、而这时平均输出电流较低。 这将确保您有足够的能量在高输出电压和低输出电压下实现 ZVS。 您将需要研究所有案例、以确保您有正确的时间安排。

我可以看到增加 Ls 为什么会有助于实现基于1/2LI^2的 ZVS。 根据您的观察、您必须调整时序。 请注意、用于设置 TABSET 和 TCDSET 的电阻器计算值仅为初始值、应根据实际设计进行调整。 我通常建议将谷底开关延迟设置为10%负载。

以下链接可为您提供应用手册、说明如何在 PSFB 桥中使用 UCC28950进行设计。 您可能会发现在为您的设计选择 Ls 和延迟时序时很有用。

https://www.ti.com/lit/pdf/slua560

此致、

你好

感谢您的联系。

当负载超过50%时、效率并不差。

我想在负载因子为20-30%时提高效率。

作为补偿、我认为在负载系数为50%或以上时可以降低效率。

对此有什么对策吗?

另外、请告知我日前我向您提出的以下问题。

增大 Ls 值会增加输出压降。

其他人的问题和答案中也有类似的陈述。

这可能是什么原因造成的?

即使我更改 CS 端子的电阻、也没有变化。

LS 为30μH、因此它并不是一个特别异常的值。

此致

您好!

在较轻负载时、开关损耗占比更大。 您可以使用更大的 Ls 来确保您具有更轻负载下的 ZVS。

我知道您目前正在处理的内容。

您还可以选择具有更低 RDS ON 和 Coss 的更好 FET。 可以选择具有较低栅极电容的 FET、这可以降低栅极驱动器上的负载并降低栅极驱动器损耗。

还有一种选择。 您可以并联已针对较低功率级别进行优化的 PSFB。 这将减少传导损耗并提高较高负载时的效率。 但是、随着负载减少、您可能需要关闭并联相。

如果您决定并联相位、则应考虑将它们交错以降低输入和输出电容器 RMS 电流。 这将减少电容器中的 ESR 损耗。

变压器的 Ls 和变压器磁化电感(Lm)构成一个分压器。 如果增大 Ls 尺寸但不调整变压器匝数比、可能会导致维持输出电压出现问题。 以下公式可用于帮助您调整变压器匝数比。

输出电压/输入 电压=(Ls)*NS/NP*Dmax

此致、