Other Parts Discussed in Thread: CSD18542KTT, CSD18540Q5B, CSD19505KTT, LM9061-Q1

主题中讨论的其他器件: CSD18540Q5B、 CSD19505KTT、 LM9061-Q1

团队、A.、您好!

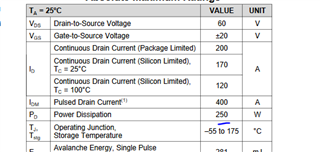

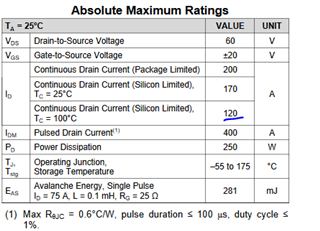

我们需要根据以下规格选择一个 N 通道。

90A 持续电流

200A 脉冲(100us)

150A 脉冲(1ms)

低 Rdson

低输入和输出电容

MOSFET 用于打开/关闭电路板电源(48V 系统)。

我可以将 MOSFET CSD18542KTT 用于我们的应用吗?

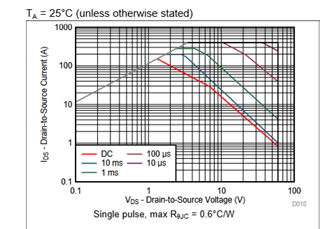

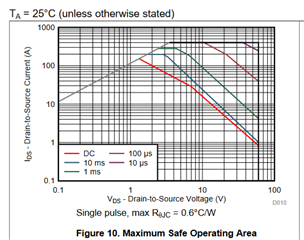

VDS 在 SOA 中有何关联。

上图显示了当 VDS 高于1V 时、直流漏极电流大于120A。

VDS 是 RDS 和漏极电流

器件的 RDS 是3.3-mΩ、ID 是90A。

因此、VDS 将仅为297mV。

请更正我是错的。

有人可以检查器件是否在 SOA 中工作吗?

正在查找您的回复