Other Parts Discussed in Thread: TPS28225

具有单引脚控制器的三态输入

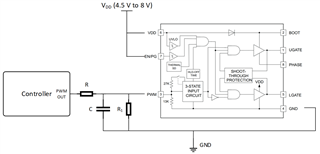

TPS28225具有一个三态输入、通过在三态窗口中将 PWM 引脚设置为高阻抗、该输入允许控制器使用单个引脚驱动两个输出 FET 以及将两个输出设置为低电平。 要仅将控制器的一个输入用于 PWM、必须将 EN/PWM 引脚连接到 VDD、并且控制器必须能够将 PG 引脚设置为高阻抗、低阻抗或高阻抗。 图1显示了单输出控制器的实现示例、其中在 PWM 信号上具有可选的 RC 滤波器、在 PWM 信号上具有可选的下拉电阻器。

图1–TPS28225三态单输入示例原理图

禁用三态输入模式

如果不需要三态模式、可以使用驱动器外部的下拉电阻器(R1)来禁用此操作。 通过将 R1设置为3.5k Ω 或更小、如果 PWM 悬空、下拉网络现在会将 PWM 引脚设置为低电平。 添加一个阻值大于40k Ω 的电阻器将确保浮动 PWM 引脚为高阻抗、并允许三态运行、但不需要 R1。 值介于3.5k Ω 和40k Ω 之间的下拉电阻器会导致三态电路意外运行、应避免使用。 PWM 引脚有一个连接至 VDD 的27k Ω 内部上拉电阻和一个连接至接地的13k Ω 下拉电阻。 此内部电阻分压器网络旨在在 PWM 悬空时将 PWM 信号拉至三态窗口。

PWM 信号注意事项

为确保正确的稳态运行、向栅极驱动器提供的 PWM 信号应遵循以下指导原则:

- 至少30ns 的输入脉冲宽度

- 干净、低噪声的方波、上升沿和下降沿的压摆率明显快于250ns 延迟计时器

- 足够的 PWM 电压电平、避免出现三态窗口。 这些电平包括1V 的低信号电压阈值和 PWM 信号振幅75%的高信号电压阈值。 介于1V 和75% PWM 振幅之间的窗口是三态窗口。

最大限度地降低 PWM 信号上的噪声

为了最大限度地减少 PWM 信号上的高频噪声、可以添加一个小型 RC 滤波器、该滤波器放置在靠近驱动器但位于可选下拉电阻器(R1)之前。 当进入三态模式时、RC 滤波器会将保持时间延长 RC 时间常数、从而影响三态电路的运行。 建议 在初始设计中为此 RC 滤波器和下拉电阻器(R1)做出配置、以便在需要时添加。

有关 TPS28225三态输入特性的更多信息、请参见数据表的第6.3.4节"三态输入"。