尊敬的先生:

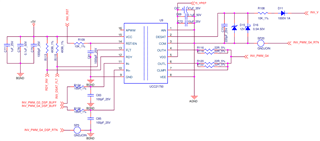

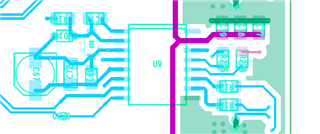

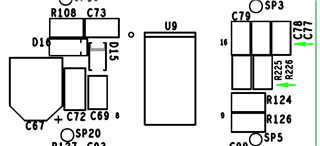

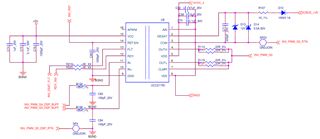

我们使用 UCC21750在三相 VSI 上测试 DSAT 功能。

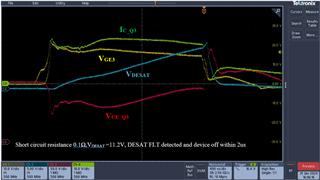

条件#1:

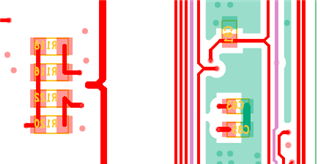

上开关脉冲和下开关短路时。

上部开关的脉冲关闭时间约为1.338us、而 DSAT FLT 报告时间约为300ns。

上部开关 VCE (C4绿色)[逆变器 G3 PWM 回路与输出 V 端子连接]

DSAT FLT (黄色)

条件2:

同时降低开关脉冲和缩短上短路。 脉冲关闭时间2.184us、DSAT FLT 再次报告时间300ns。

对于下部开关

下部开关 VCE (C4绿色) [逆变器 G4 PWM 回路与输出直流母线连接]

DSAT FLT (黄色)

我使用了100pf 作为 C BLK 。 和计算的 tBLK 时间约为1.8us。 如果我们添加 "前沿消隐时间" tDESATLEB 约200ns 和 tDESATOFF (tDESATOFF) ("DESAT 传播延迟到 OUT (L) 90%时间")~300ns。 所需的总时间约为2.3us。

但我的上部开关低电平脉冲在1.338us 内。

请告诉我们为什么我们会遇到两次不同的问题。