您好、TI 团队、

我 在我们的项目中使用了多个 TPS568230RJER 器件。

此模块面临几个问题、请仔细阅读以下问题陈述-

问题- 1:即使未提供使能、稳压器的输出电压也会出现斜坡。

实际上、我们使用同一器件(TPS568230RJER)推导 FPGA 的电源(1V、1.8V、1.5V、3、3V 等)。 将这些器件的使能引脚和电源连接起来以实现所需的电源时序。

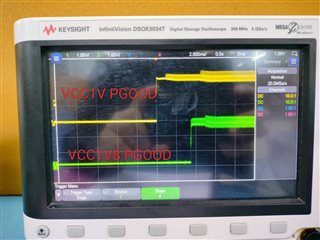

在这里、我们将仅讨论其使能引脚由1.8V 稳压器的电源正常状态驱动的3.3V 稳压器。 但是、这个3.3V 稳压器的输出电压在从1.8V 稳压器获得其使能信号之前开始上升大约40-60ms。 在这40-60ms 的持续时间内、此斜坡电压从0V 上升到0.9V。

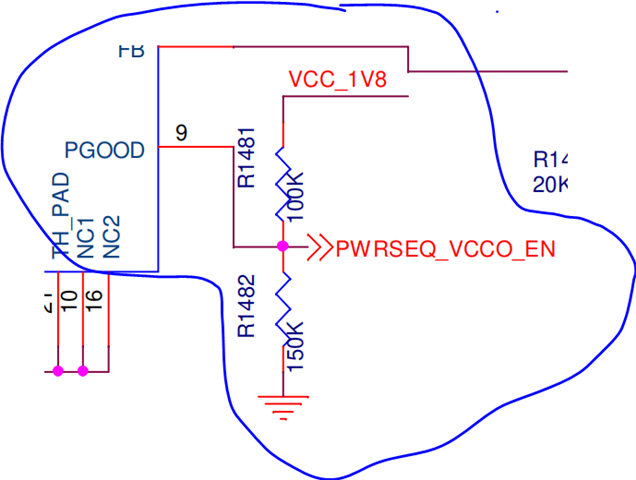

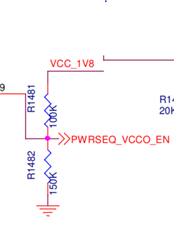

请找到相应原理图的快照、供您参考-

因为使能引脚不会接受高于3.6V 的电压、所以分压器电路在1.8V 的电源正常上施加(介于 VCC 和接地之间)。

3V3稳压器的输出波形可在下图中看到-

问题2:当我探测稳压器的 VCC 引脚时、该引脚是内部 LDO 的输出引脚。 我观察到了纹波、请参阅下图-

请尽快进行调查、因为我们在调试时遇到这个问题、并且相同的器件型号也用于其他进行中的项目。

谢谢!

R·库马