大家好!

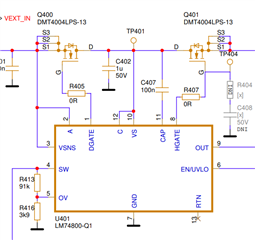

我将原理图中的 LM7480-Q1 用作理想二极管 IC 以及两个输入源之间的输入源选择电路。 不过、在测试 IC (仅一个通道、不在两个输入源之间改变)时、我只是注意到了一个奇怪的行为。 一旦 EN/UVLO 引脚被拉高(3.3V)、IC 就可以正常工作、但当我尝试禁用它时(将 EN/UVLO 拉至0V 低电平)、DGATE 和 HGATE 驱动器信号保持高电平! 我已使用我的两个输入源单独对其进行了测试、即使电路相同、也遇到了差分行为:

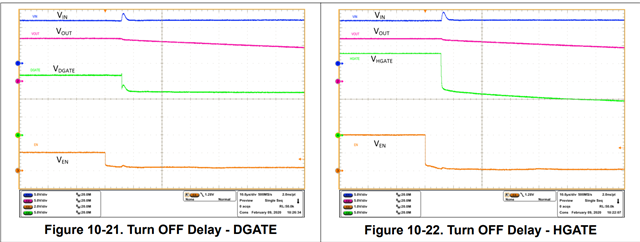

- 24V 输入源: 当 EN/UVLO 引脚被拉低(0V)时、DGATE 信号仍然为高电平、但 HGATE 信号被拉低(DGATE 信号也应该发生这种情况)。

-蓄电池输入源(约23V): 当 EN/UVLO 引脚被拉至低电平(0V)时、DGATE 和 HGATE 信号仍为高电平。

我对其进行了检查、发现 EN/UVLO 电压在两种情况下都恰好为0.0V、以检查其是否低于最小 V (ENF)电压(根据数据表、为0.3V)。 在这种情况下、LM7480-Q1应进入关断模式、同时禁用两个栅极驱动器、但显然无法按预期工作。 下面您可找到24V 输入源的原理图(作为示例):

在这种情况下、安装 R404和 C408以减小浪涌电流(分别为100 Ω 和22nF)。

我希望这些信息足以帮助您确定问题的根源。 非常感谢您的参与、期待您的回复。

此致、

胡安