Other Parts Discussed in Thread: UCC12051-Q1, AMC1351, UCC12040, UCC12050EVM-022, UCC12050

主题中讨论的其他器件: UCC12050EVM-022、 UCC12050、AMC1351、UCC12051-Q1

您好!

我有关于 UCC12040的三个问题。

问题1: 与内部时钟单独使用。 如果 SYNC (4引脚)短接至 GNDP、是否没有问题?

问题2. 在 Q1情况下、SYNC_OK (5引脚)终端处理100kΩ 上拉还是开路?

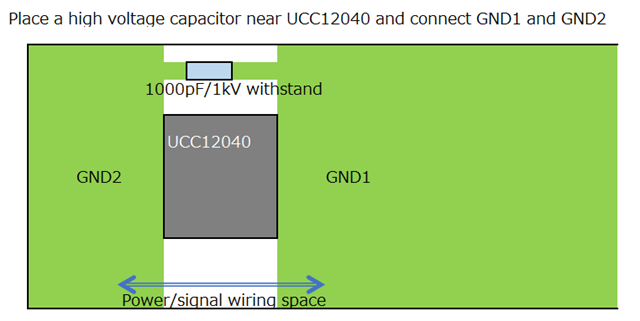

问题3: UCC12050EVM-022中 GNDP 和 GNDS 之间插入了 C5、这意味着什么? (LYR2-LYR3层间缝合盖)

谢谢。

科诺