你好。

我们正在使用评估板 TPS23525EVM-815对 ORing 电路进行实验。

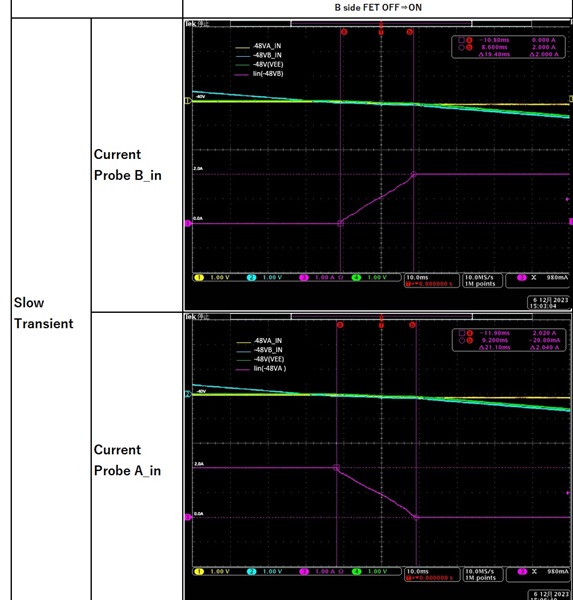

在向 A 输入端施加-40V 恒定电压的情况下、我们已逐渐增大 B 输入端的电压、以查看在开关点是否存在从 A 输入端到 B 输入端或从 B 输入端到 A 输入端的直通电流。

当 B 输入的电压变化缓慢时,没有电流流经,。

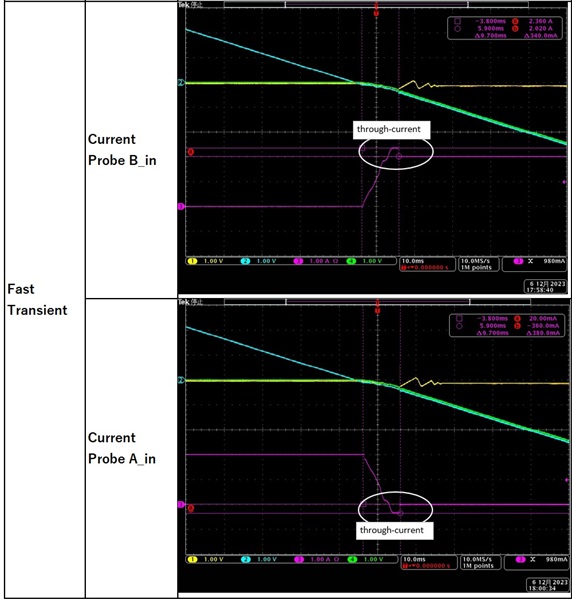

但当快速改变时、似乎瞬态流过电流会瞬间流动

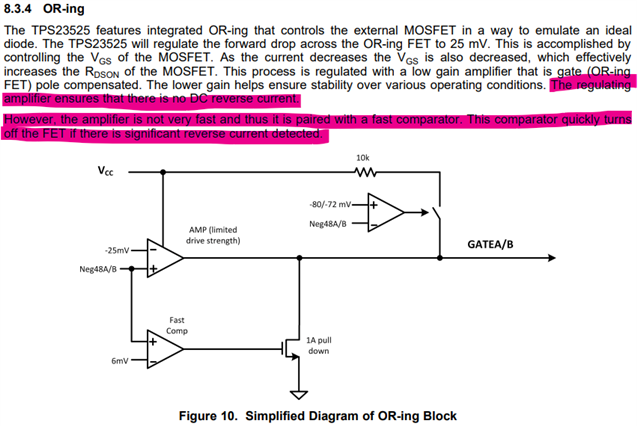

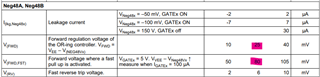

Q1请说明 TPS23525内部的预防机制如何防止流经 A 输入端或从 B 输入端流向 A 输入端的电流。

Q2请解释在快速切换时为什么会出现瞬态馈通电流、以及 Q1中提到的预防机制在这种情况下是如何工作的。