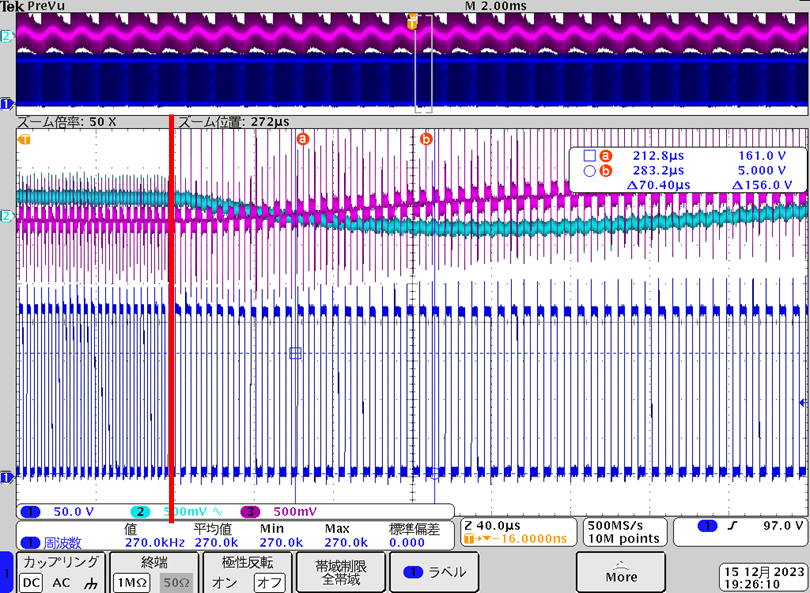

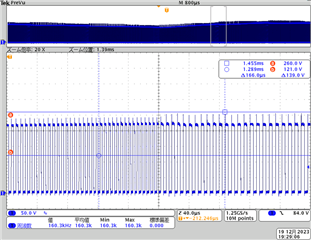

请检查下面的波形。

CH1 (蓝色)是低侧 FET 的 VDS。

从红线部分看、高侧 FET 的导通时间瞬间变长。

高侧 FET 的导通时间持续很长、输出电压(CH2:淡蓝色)降低、光电耦合器集电极和发射极(CH3:紫色)之间的电压提高。

我将 RTZ 和 RDM 的电阻值更改了±10%、但运行中没有变化。

您能想到为什么高侧 FET 的导通时间瞬间变得更长的原因吗?

到目前为止、我已经制造了500多个器件、只有一个出现了这个问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

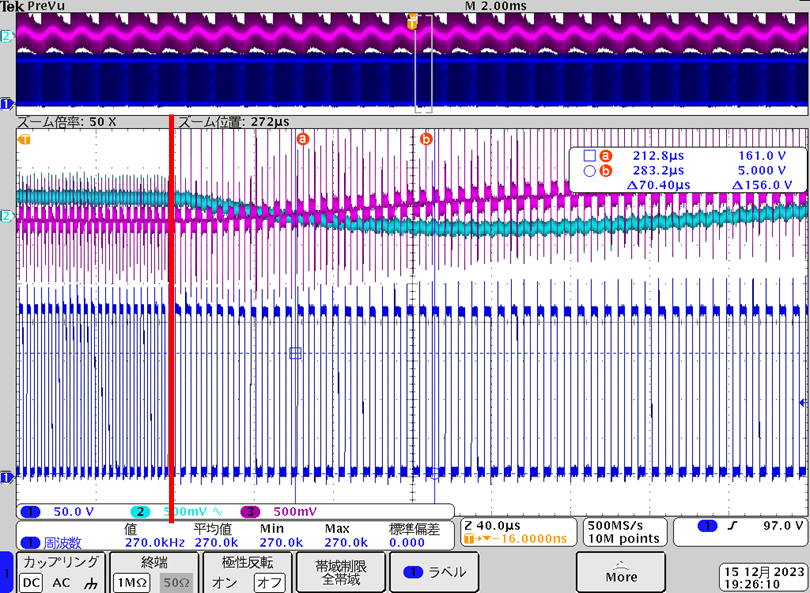

请检查下面的波形。

CH1 (蓝色)是低侧 FET 的 VDS。

从红线部分看、高侧 FET 的导通时间瞬间变长。

高侧 FET 的导通时间持续很长、输出电压(CH2:淡蓝色)降低、光电耦合器集电极和发射极(CH3:紫色)之间的电压提高。

我将 RTZ 和 RDM 的电阻值更改了±10%、但运行中没有变化。

您能想到为什么高侧 FET 的导通时间瞬间变得更长的原因吗?

到目前为止、我已经制造了500多个器件、只有一个出现了这个问题。

尊敬的 Takuya-San:

感谢您对 UCC28782的查询。

我想就这一点发表评论真的很难。

对于 UCC28782控制器、实际通过将峰值初级电流(峰值电流模式控制)控制到内部电流检测阈值电压(Vcst)来设置占空比。

PWML 信号在开关周期开始时设置为高电平、并保持高电平、直到 CS 输入端的电压超过内部阈值。 Vcst 本身通过 FB 引脚上拉的电流根据器件的控制律进行调制。

驱动有源钳位晶体管的 PWMH 信号也会部分基于退磁时间(由峰值初级电流、输出电压和匝数比决定)间接调制、部分基于根据输入电压产生负磁化电流所需的任何额外时间进行间接调制。 由于您没有通过更改 RTZ 和 RDM 观察到任何影响、因此我怀疑这可能是由 FC/CS 信号产生的噪声导致控制器的时间突然变化所致。

您观察到此问题的条件是什么-输入电压和负载条件?

此致、

哈里什

在整个输入范围内、直到 LPM 的运行都没有问题、但从进入 ABM 后就会出现异常运行。

上面的波形是发生此问题的 IC ABM 工作范围内低侧 FET 的 VDS 波形。

与之前的导通时间相比、高侧 FET 的导通时间迅速增加。

μs 波形经过几 μ s 后的波形如下所示、SW 操作次数从2变为5、最终执行 AAM 操作。

如果此故障 IC 安装在正常工作的电源上、则会出现上述故障症状。

因此,我们认为没有噪声因素。

如果是噪声因素、可以考虑采取哪些对策?

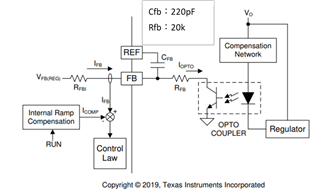

FB 引脚的电路配置与推荐的电路类似(请参阅下文)。

此外、CFB 靠近板上的 IC、因此很难再靠近它。

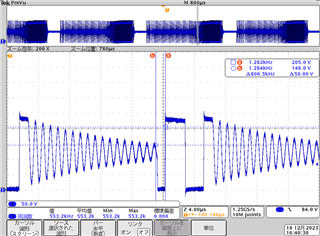

在发生此问题的 IC 处于 AAM 工作期间的波形如下所示。

在 AAM 下运行时、与 ABM 模式一样、高侧 FET 在红线区域的导通时间会突然变化、并且运行变得不稳定。

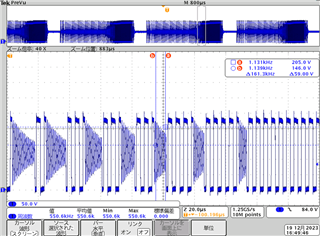

接下来、输入 DC130V 时低侧 FET 的 VDS 和 CS 端子(≒低侧 FET 漏极电流)的波形如下所示。

即使低侧 FET 的导通时间突然变化、漏极电流的峰值也不会改变。

如果 FB 引脚由于噪声等而发生变化、漏极电流峰值也会发生变化、因此 FB 引脚不可能由于噪声而发生变化。

此致、

青木拓也

尊敬的 Takuya-San:

我同意这可能不是因为我最初所想的 FB 噪音。

因此、关于在高达 LPM 区域内运行的稳定问题、我认为在 LPM 和 ABM 之间切换时、可能会存在一些边界上的不稳定性。 您能 ΔVBUR 一下 Δ Σ(LPM)是否设计为大于100mV。 当从 LPM 转换到 ABM 时、VBUR 阶跃更高时、ABM 中的初始峰值磁化电流会降低、并且每个开关周期的能量更低。 这可能会降低输出电压。 同样的事情需要检查从 ABM 模式到 AAM 模式的转换。

其次(我不是说这是原因,但你可以验证这一点) RDM 电阻器应该提供功率级信息给优化器内部的 PWMH 信号的自动调谐,以实现 ZVS。 因为 RDM 是磁化电感、RCS 和匝数比的函数。 由于我们的大多数器件都在工作(49/50)、您能否检查变压器电感中是否有任何可引起此效应的较大容差。

谢谢!

此致、

哈里什

尊敬的 Takuya-San:

谢谢你的答复。

您可能会查看以下文档、其中建议在模式之间转换时添加迟滞。

我不确定这是否能解决这一特定电路板的问题、但也可以进行尝试、因为所有其他电路板都能正常工作。 这可能是由于组件之间的部件差异造成的。 您也可以考虑尝试使用其他电路板上的任何其他 UCC28782 IC、以防将其视为原因。

此致、

哈里什