主题中讨论的其他器件: UCC21750、 UCC21710

大家好、

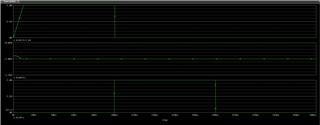

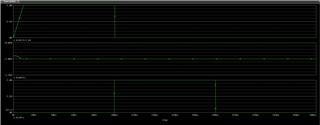

我目前正在从事隔离式栅极驱动器设计、并使用 UCC21732-Q1控制 MOSFET。 在 PSPICE 中执行仿真时、我看到 GATE 保持高电平状态、当 IN+将状态从低电平变为高电平时、FLT 引脚变为低电平。

可能是什么原因?

如有任何建议、请联系 UCC21732-Q1DW_TRANS。

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我目前正在从事隔离式栅极驱动器设计、并使用 UCC21732-Q1控制 MOSFET。 在 PSPICE 中执行仿真时、我看到 GATE 保持高电平状态、当 IN+将状态从低电平变为高电平时、FLT 引脚变为低电平。

可能是什么原因?

如有任何建议、请联系 UCC21732-Q1DW_TRANS。

谢谢。

Anand、您好!

我认为原因可能是初级侧和次级侧的电源-它们好像是与一个1kV 的电源连接在一起;这也解释了当您对照初级侧 GND 测量栅极电压时栅极电压为-1kV 的原因。 此外、当 IN+导通时、更难判断栅极是否实际正在开关。

您可以首先尝试将两个 GND 连接在一起、然后查看仿真是否正常运行;我还建议探测 OC 引脚、因为 OC 引脚上的过压会导致 nFLT 引脚变为低电平。

希望这对您有所帮助!

谢谢。

薇薇安

Anand、您好!

在这种情况下、我将查看 OC-AS DESAT 电路的设计以及系统中其他元件的参数。 例如、可以查看栅极驱动器导通时 FET 的 VDS 电压;如果 FET 在初始导通期间的 VDS 超过 DESAT 检测阈值并且消隐电容器很小、这可能就是 DESAT 触发的原因。

您可以使用 产品页此处链接的 UCC217XX 计算器计算 检测阈值和消隐时间。

或者、您可以尝试使用 UCC21750仿真模型。 UCC21750具有具有具有前沿消隐时间的 DESAT 功能;这意味着它将在栅极导通后的前~200ns 内忽略 VDS 过压、以防止 DESAT 误触发。

希望这些建议对您有所帮助!

谢谢。

薇薇安

Anand、您好!

来回答您的问题-

1.这两种方法都取决于 FET/IGBT 的 VDS/VCE 来检测过流和短路情况。 这两种方法的检测时间略有不同、所需的外部元件也不同。 通常、OC-AS DESAT 需要额外的电流来为消隐电容器充电、而 DESAT 本身的 DESAT 电流为500uA。 您可以根据自己的喜好选择这两种方法。

2.米勒钳位是任一种推荐的方式,无论您是否使用了负偏置电源。 原因在于、即使有负偏置电源、电路板耗散与米勒电容相结合、也可能产生超过阈值电压的电压尖峰。 对于此智能隔离式栅极驱动器系列、如果您不想使用外部米勒钳位 FET、我们会提供内部米勒钳位版本(例如 UCC21710和 UCC21750)。

OCDET 检测阈值是使用 此处提到的方法计算的、基本上要考虑各种外部组件(电阻器、二极管等)上的压降

希望这对您有所帮助!

谢谢。

薇薇安

Anand、您好!

我不确定您刚才谈到的具体分析、或许您可以在 PSpice for TI 论坛中发布另一个问题、专家可以帮您解决。

VOCDET 指 OC 引脚触发的 VDS/VCE 电压。 OC 引脚始终在~0.7V 时触发和启动软关断/两级软关断、但对于不同的外部元件、 发生关断事件的 VDS/VCE 阈值不同。 因此、您应该找到一个可将 FET/IGBT 短路的 VDS/VCE 电平、并调整外部元件值、以确保在所需的 VDS/VCE 电压下触发 OC。

谢谢。

薇薇安

Anand、您好!

从理论上讲、如果所有 FET 和栅极电阻器具有完全相同的参数、则应该不会成为问题。 但在现实生活中、它们从来都不是完全相同的、并且 FET 放置在 PCB 上的不同位置、因此 PCB 的不同寄生电容/电感也会起作用。

我认为-尝试通过稍微改变每个 FET 的 FET 参数(内部栅极电阻、栅极电容等)来模拟它。 如果没有发生重大问题、您可以在实际的 PCB 中尝试这种方法。 最坏的情况是栅极振铃会破坏正常性能;在这种情况下、您可以选择不使用 CLMPE、因为您具有+15V/-8V 双极电源。

薇薇安