主题中讨论的其他器件:TINA-TI

大家好、

我最近从事的是栅极驱动器设计、我 计划 将其用于 UCC5350MCD 部件. 我已经在 LTSpice 中设计了电路、并尝试对其进行仿真、到目前为止没有出现任何误差、但输出不符合我的预期。 我在 MOSFET VDS 上得到一个较小的持续浪涌(正常瞬态浪涌除外)。 我曾尝试更改死区时间和栅极电阻器值、但仍然没有看到任何改善。

如果有人能指出我错了什么,那将会很有帮助。

提前感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我最近从事的是栅极驱动器设计、我 计划 将其用于 UCC5350MCD 部件. 我已经在 LTSpice 中设计了电路、并尝试对其进行仿真、到目前为止没有出现任何误差、但输出不符合我的预期。 我在 MOSFET VDS 上得到一个较小的持续浪涌(正常瞬态浪涌除外)。 我曾尝试更改死区时间和栅极电阻器值、但仍然没有看到任何改善。

如果有人能指出我错了什么,那将会很有帮助。

提前感谢。

Anand、您好!

这种 VDS 尖峰是电源设计中需要解决的一个重要问题、因为它会损坏您的开关或迫使您使用比所需更昂贵的高压开关。 V= L * di/dt。 添加栅极驱动电阻器将增大开关 dt 并减小 di/dt。 您确实需要大幅增加 dt 来减缓小 Cgate 的栅极电荷、这也会增加开关损耗。

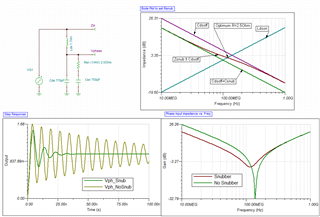

我更喜欢的一种解决方案是在电源轨上添加缓冲器。 这主要是为了阻止开关节点来回振铃、但确实可以稍微降低尖峰振幅。 我附上了一个 TINA-TI 示例、说明如何针对给定的额定功率优化缓冲器电阻值。

另一种可确保开关不受过压影响的方法是使用 TVS 二极管。 这不是常用的解决方案、但它们是防潮的、允许您使用非常接近 FET 额定电压的电压。

另一种解决方案是使用接地/电源平面。 这将大大减少电感、并减少下冲/过冲。 一旦有了低电感平面、在出现的瞬态电压下添加钳位二极管要容易得多。

此致、

肖恩

e2e.ti.com/.../0474.GateRing3.TSC

P.S.、请记住、闭合开关不受过压影响。 如果您看到短路的两个引脚上出现高电压振铃、则可能是在测量寄生电感器而不是硅上的电压。

您不会希望将缓冲电路添加到开关节点本身上。 它必须在每个周期充电和放电至高电压、并会消耗大量电力。

最有效的缓冲器是位于局部去耦电容器上的缓冲器。 当高侧开关闭合时、它会对开关节点短路。 这可以让您抑制谐振、而无需使用电容器来循环高电压。 您可能需要两个缓冲器:一个用于缓冲 FET 封装的漏极电感、一个用于缓冲电池或大型去耦电容器中的整体电源电感。 它们将在两个不同的频率振铃。

缓冲器不会对初始峰值钳制太多是正确的、但您确实需要消除共振。 它可能耦合到栅极驱动器中并导致损坏。 它还会减小 PWM 的可用占空比。

为了消除峰值、您应该尝试使用 TVS 钳位二极管。 它们吸收第一个峰值、如果开关节点+电源为微伏阻尼、电压将以极小的振铃恢复到正确的值。 IGBT 具有自然的雪崩击穿、能够吸收这些峰值(在合理范围内)、与 SiC 相比、这是一个显著的优势。 如果可以牺牲开关和导通损耗并且非常关注过压、那么值得关注。 不过、通常首先考虑开关损耗、最好使用 TVS 二极管来解决该问题。

请注意、与迹线相比、电源平面的电感要低得多。 这会将谐振频率提高到可通过低寄生串联电阻获得更好阻尼的水平、因此将降低峰值电压。

此致、

肖恩