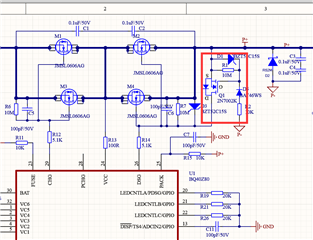

连接图中红框所示的反向电路后、测试短路保护没有恢复、如果仍然连接到通信端、通信相关元件会烧坏、原因是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

连接图中红框所示的反向电路后、测试短路保护没有恢复、如果仍然连接到通信端、通信相关元件会烧坏、原因是什么?

您好!

反向电路保护不应影响 OCD 事件的恢复。 我们的电路与我们的不同之处在于、我们只能发现传统二极管(D6)在10k 以上、而不是在我们的设计中。 这不会导致您遇到的问题。

在添加反向电路保护之前、您是否进行了短路测试?

如果短路保护仍然连接到通信,则与通信相关的组件将被烧毁

您是指 SMBus 通信线路中的组件? 如有可能、请分享整个原理图。 这听起来 FET 在短路测试期间保持开路。

此致、

何塞·库索

您好!

只是为了澄清一下、电路是反向充电器保护电路、而不是短路保护电路。

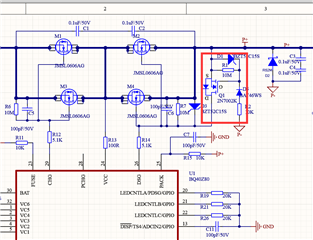

您添加的电路和我们在 EVM 中的电路没有太大差异。

我确实看到有几件事 可能需要改进。

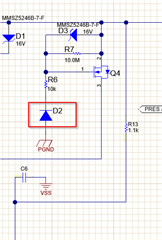

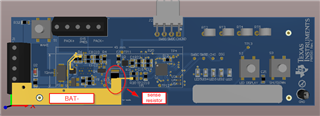

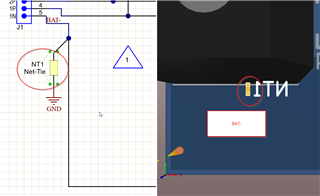

1-我们建议将低电流路径(IC GND)与高电流路径(BAT-)分开。 我们通常通过添加网络连接或0欧姆电阻器来实现这一点。

请参阅下面的 EVM 示例。

2、建议在 FET 的每个栅极添加一个10欧姆。 这是为了避免振铃和振荡。 请参阅此 应用手册以获取最佳建议指南。

此外、请参考这一 线程在其中讨论了短路测试期间的常见 FET 故障。 请注意、这是一款不同的器件、但原理相同。

最后、您可能需要在我们的 EVM 中测试短路测试、然后查看是否可以重现该问题。

此致、

何塞·库索

您好!

当并联放置时、会在每个充电和放电 FET 的栅极施加10 Ω 电阻。 https://www.ti.com/lit/an/slpa020/slpa020.pdf

我在原理图之间没有看到重大差异。 但有时很难找到差异、或者可能是布局问题。 尝试在评估板中进行测试有助于消除多个根本原因。

此致、

何塞·库索

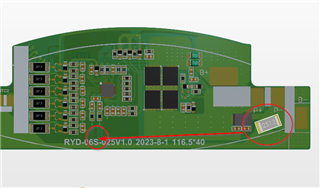

e2e.ti.com/.../RYD_2D00_06S_2D00_025-V1.0.rar

这些是我的原理图和 PCB 文件。 除了上述两点外、您能否检查 PCB 布局以了解哪些地方需要改进?

非常感谢!

您好!

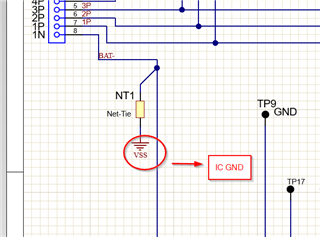

请看布局。 请查看我的以下评论。

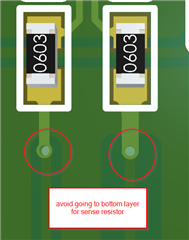

1-建议检测电阻应足够靠近 IC。 远距离会带来噪声并更容易受到 ESD 的影响。

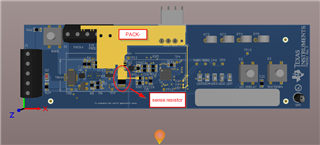

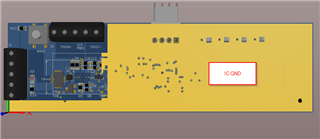

2-建议将高电流路径(BAT-)与低电流路径(GAUGE IC GND)分开。 请参阅下面的示例

请注意上面的 检测电阻 线路是如何隔离的。 这有助于实现库仑计数器的抗噪性能。

请注意我们如何使用网络连接将 BAT-从 IC_GND 分离、

转到 检测电阻线路的底层会增加 ESD 和噪声敏感性。

其余的看起来不错。 我看到输入单元 RC 滤波器足够靠近 IC。

此致、

何塞·库索