主题中讨论的其他器件: TINA-TI

图1所示的驱动方法不需要使用 PWM 来驱动信号。 我们能否持续保持 HO 输出高水平、而 LO 持续输出低水平?

图1

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

图1所示的驱动方法不需要使用 PWM 来驱动信号。 我们能否持续保持 HO 输出高水平、而 LO 持续输出低水平?

图1

谢谢

Liujun,

很抱歉由于美国度假而导致响应延迟。

在回答您的问题时、这取决于 HS FET 的浮动电源。 在通常使用的自举电路中、浮动电源由一个需要关断时间进行再充电的电容器保持(它基本上是开关电容器电路的非常基本的版本)。 但在您提供的图像中、浮动电源未定义。 因此、无法判断 HS 是否可以无限期保持开启。 从 FET 的角度来看、使 HS 始终保持开启状态、使 LS 始终保持关闭不会成为问题。 显然、您需要避免两者同时导通、以避免击穿/短路。

谢谢

克里斯

您好 Liujun:

再次感谢您关注 TI FET。 为了保持高侧 FET 处于开启状态、您必须在栅极上施加至少比连接到漏极的直流输入电压大4.5V 的电压。 当 FET 导通时、漏极和源极电压大致相等、因此 VGS = Vgate - VDRAIN、必须> 4.5V。 请注意、持续保持 HS 开启将使电感器饱和、这可能会导致过大的电流流过 FET 并损坏它。

此致、

约翰·华莱士

TI FET 应用

尊敬的柳军:

通常、所有 MOSFET 数据表都规定了 VGS 的最小值、其中测试和保证了 RDS (on)。 这适用于所有 TI FET、包括 CSD18511KCS 数据表(其中规定了 Rds (on)在最小 VGS = 4.5V 时的规格)。 正如我在之前的响应中所解释的、当 FET 开启时、漏极和源极电压大致相等。 对于源极未连接到 GND 的高侧开关、必须将栅极电压上拉至高于漏极电压(因为 VDRAIN≈Vsource)的最小 VGS 值(数据表中指定了 RDS (on))。 电压可能会更高(始终达到数据表中规定的绝对最大值、即 CSD18511KCS 的20V)。 通过在栅极和源极之间施加电压而不是在栅极和漏极之间来接通 FET。

谢谢。

约翰

尊敬的柳军:

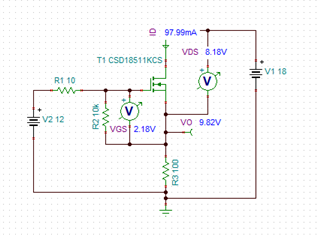

在您的电路图中、FET 将在饱和区(Vds > Vgs - Vth)运行。 这也称为线性模式操作。 我创建了附加的简单 TINA-TI 仿真来估算电路的直流运行条件。 对于典型器件、VO = 9.82V、VGS = 2.18V、VDS = 8.18V 且 ID = 98mA。 为了保证 FET 导通、VGS 必须至少为4.5V。 如果电池电压显示为23V、那么 FET 将被完全打开:VO = 18V、VGS = 5V、VDS = 498μV Ω、而 ID = 179.5mA。

此致、

约翰

尊敬的柳军:

IGBT 类似于 MOSFET。 栅极发射极电压必须被驱动至足够高的电压、以最大程度地减小集电极-发射极电压。 在电路图中、蓄电池以发射极端子为基准、VGE 应为大约12V。 我拉取了图表中 IGBT 的数据表、它指定了 VGE =15V 时的 VCE (SAT)。 观察数据表中的图1、在 VGE = 12V 时、VCE (SAT)似乎会更高一些。 集电极处的电压为700V 时、电池不应损坏。 我建议联系 IGBT 供应商获取更详细的技术帮助、因为 TI 不生产 IGBT。

谢谢。

约翰