您好!

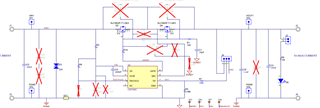

我在设计中使用 LM74502作为输入反向保护。 下面是部分原理图。 在我的测试中、24V 直流是输入电压、没有负载连接到输出。

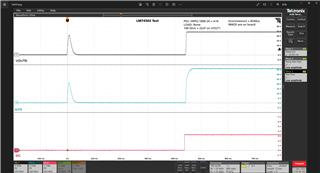

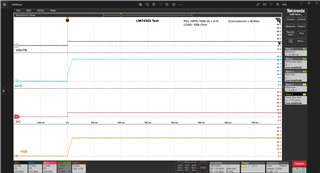

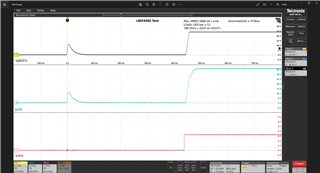

我发现上电时输出电压出现异常。 在输出电源完全启动之前、输出电压上有一个小凸点、如下图所示。 "SHDN"信号连接到 LM74502的 EN/UVLO 引脚。 从图中可以看出、在输出电压上发生碰撞后、"SHDN"信号变为高电平超过400ms。

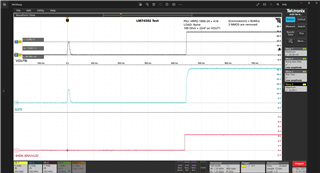

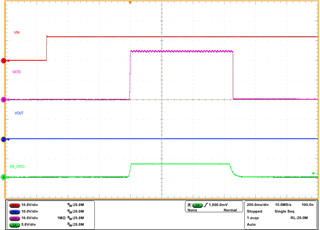

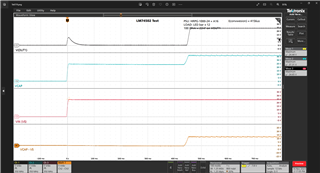

然后、我检查了 VS、这是我们设计中的输入电压、以及 VCAP。 从图中可以看出、VCAP 和 VS 之间的电压在输出电压发生碰撞后超过400ms 后也变为有效、如下图所示。

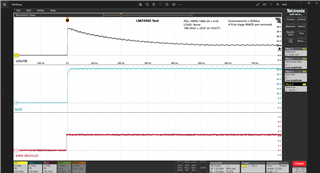

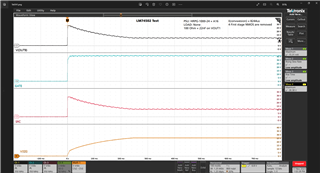

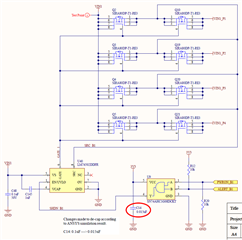

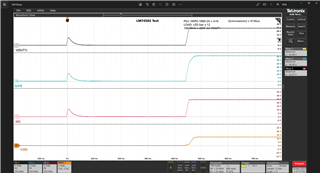

我还测量了 LM74502的 GATE 和 SRC 引脚上的电压、如下所示。 根据 V (GS)、外部 NMOS 应在我们的预期时间打开、距离碰撞超过400ms。 实际上、该凸点也会出现在栅极和 SRC 引脚上。

根据这些测试结果、我认为 LM74502的电荷泵和栅极驱动器按设计工作。 输出电压、GATE 和 SRC 引脚上的凸起似乎是耦合的结果。 您以前是否在使用 LM74502的其他电路中发现过这种现象? 耦合路径是否可能位于这些外部 NMOS 内部? 是否有办法解决这种问题?

谢谢!