您好!

我在电路中使用 LM74502作为反向保护。

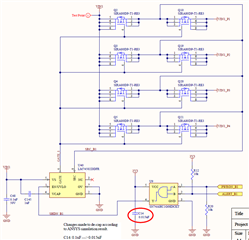

下面是 LM74502部分的原理图。 VIN 上有一个 TVS (SMA24CA-13-F)、电路板上没有用于 VOUT (原理图中的 VIN1_P1至 VIN1_P4)的输出电容器。 不过、这四个输出电源是为用户设计的、因此用户可以将其负载连接到我们的电路板。 负载上可能存在输入电容器、这些电容器实际上是 LM74502的输出电容器。 我们只是无法控制它们的电容。 VIN 的电压范围为5V 至24V。

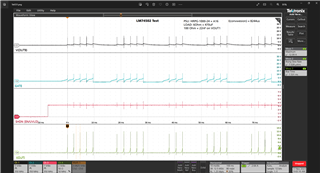

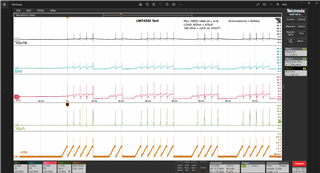

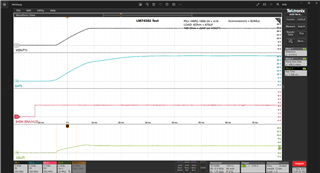

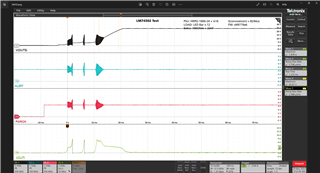

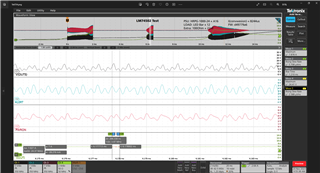

在我的测试中、我使用24V 作为输入电压、使用与470uF 电容器并联的6 Ω/300W 电阻器作为负载来模拟实际情况。 我注意到在上电时、VOUT、IOUT 和其他一些信号上存在一些尖峰。 请检查下图、并在100ms 后忽略这些波动。 它们可能是由原理图中的"PWRON_B1"信号引起的。 在这个阶段、我只是想了解上电过程中的这些尖峰。

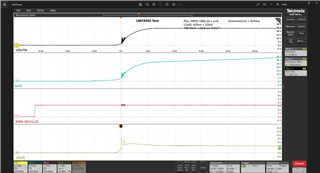

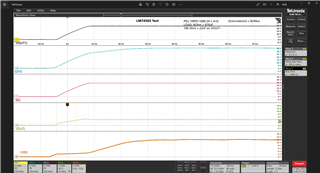

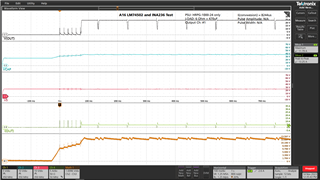

上述情况仅在470uF 电容器与6欧姆电阻器并联时发生。 移除电容器后、可以非常平稳地启动 VOUT 和 IOUT、下图显示了当电容器不存在时 VOUT 和 IOUT 的波形。 请忽略这些负脉冲。

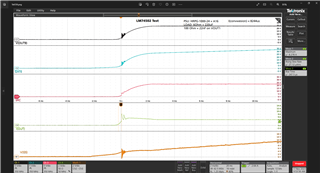

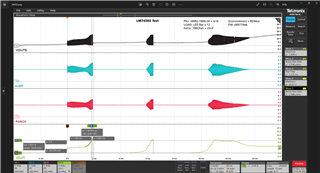

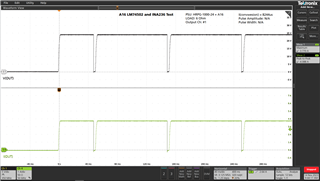

这使我觉得尖峰是由浪涌电流引起的。 另外从第一张图可以看到、"VCAP-VS"(底部的数学通道)在上电过程中难以达到11.6V、它的波动与 VOUT、IOUT、VCAP 和 VS 上的尖峰保持同步、 从 LM74502的 GATE 引脚到 GND、我添加了一个100欧姆电阻器与一个2.2nF 电容器串联、如数据表中的第8.3.3.1节所述、尝试提供额外的浪涌电流控制。 看来这种修改顺利地增加了输出功率、如下图所示。

我的问题是:

1.浪涌电流是否是这种加电不稳定的根本原因?

2.如果上述问题的答案是肯定的、为什么浪涌电流会让 LM74502出现这样的行为? 使用浪涌电流时、为什么信号"VCAP-VS"(因此、VGATE)无法立即达到设计值?

谢谢!