主题中讨论的其他器件: 3220UFP-DGLEVM

您好、专家!

我使用 HD3SS3220为 USB Type-C 接口设计电路板、并检查了波形和功能。 我在 CC1、CC2端口上发现了一些奇怪的行为。

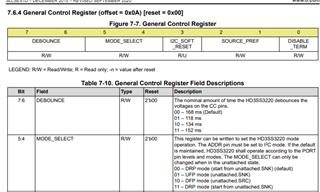

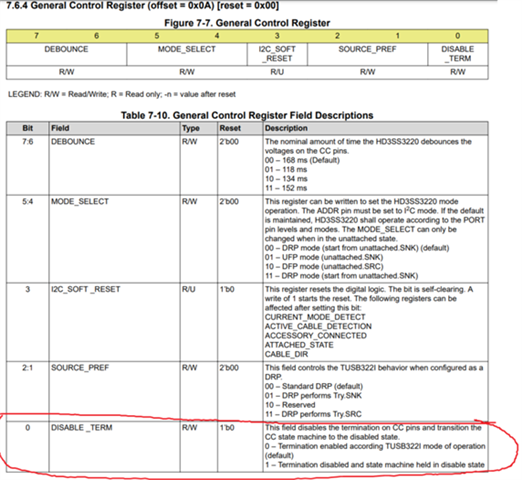

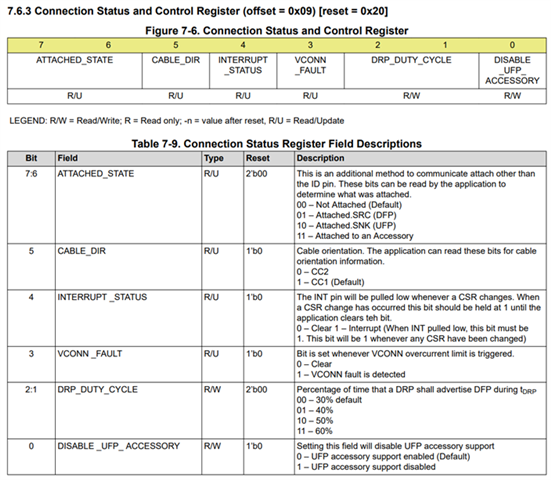

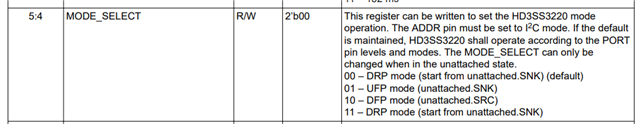

我将电路板设计为 UFP 并按如下方式设置端口(我附加了部分原理图)

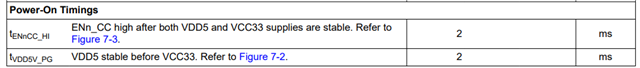

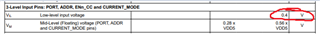

端口:GND、 ENN_CC:GND

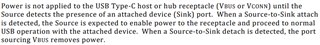

现在、我未连接任何 USB 电缆、即 CC1和 CC2已打开、其中不包括它们上面的 ESD 无源器件。 我认为 CC1和 CC2都具有内部下拉电阻器、约5Kohm 用于检测 Type-C 旋转、但我观察到4.5V 脉冲、周期为80ms。 我在附加的 jpg 文件中将其显示为(1)。 似乎没有下拉电阻器。 我尝试在 CC1和 GND 之间在外部添加4.7千欧、然后降低至344mV 的脉冲电平。 它们显示为(2)和(3)。 那么、我认为没有内部下拉电阻器。 此80ms 周期噪声会在某些情况下出现在 VBUS 上、当然、没有 USB 连接。 我想它是由任何噪声传导引起的。

我的设计是否有任何错误、或者 此行为是否正常?

此致、

Terry、