主题中讨论的其他器件:TIDA-010057、

参考设计:TIDA-010057已创建并评估。

请告诉我以下有关 Vin 从5V 降低时的操作情况。

・由于 FET 的特性、当电压降至 VG 阈值以下时、在 Vin 约为4.3V 时、将停止运行、但电压存在变化、例如3.8V。

(运行停止时、两个漏极电流均为0.6A。)

除了 FET 特征错误、LM3488内部是否有任何控制?

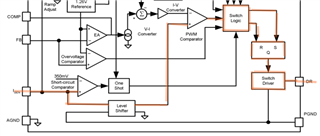

我很好奇下面的内部方框图中的开关驱动器所执行的控制方式。

・此电路正常运行是否有必要的漏极电流值?

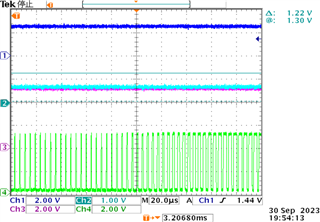

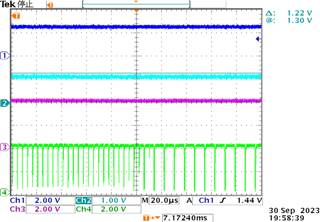

停止运行过程中、・Duty 和 Fsw 发生变化。 对 DR 引脚进行了什么类型的控制更改?

※CH1:VIN、CH2:VBUS、ch3:ISEN、CH4:Dr

・您能否提供以下内部电路的详细操作信息(橙色)?

我特别想了解电平转换器、开关逻辑和开关驱动器块中的具体操作和电路配置。

特别是如果内部电路不能正式公布、请直接通过电子邮件与我联系。

此致、

聪