Other Parts Discussed in Thread: TPS51206

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS51206 大家好!

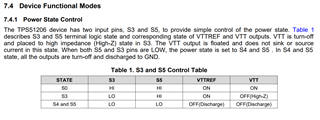

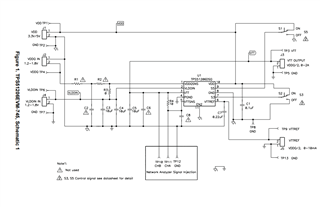

我正在研究在1.2V 逻辑下将 TPS51206用于 DDR4应用。 数据表的第7.4.1节列出了控制器件所需的电源状态、但关于这两个引脚我有一些要求:

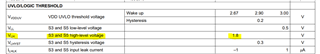

1.如何针对1.2V 逻辑正确端接 S3和 S5引脚?

2.使用 S3和 S5引脚的 DDR4的正确逻辑控制是什么? 数据表中未明确定义 HI 和 LO 状态所需的电压电平为1.2V。

请尽可能告诉我您的想法、希望能尽快收到您的回复