主题中讨论的其他器件:UCC27200、、 UCC28521

大家好、

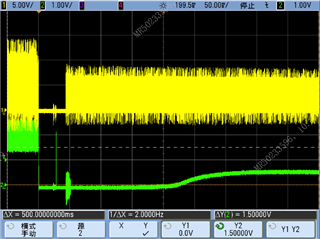

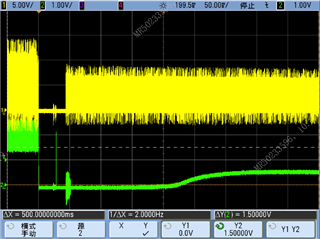

客户设计 UCC28251和 UCC27200、如图所示。 客户发现、当 UCC28251的 EN 引脚低于1.5V 时、UCC28251的输出仍输出驱动信号。 您可以帮助对其进行评论吗? 绿色波形是 EN、黄色波形是 UCC28251的输出信号。

e2e.ti.com/.../half_2D00_bridge.pdf

谢谢!

雷纳

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

客户设计 UCC28251和 UCC27200、如图所示。 客户发现、当 UCC28251的 EN 引脚低于1.5V 时、UCC28251的输出仍输出驱动信号。 您可以帮助对其进行评论吗? 绿色波形是 EN、黄色波形是 UCC28251的输出信号。

e2e.ti.com/.../half_2D00_bridge.pdf

谢谢!

雷纳

您好!

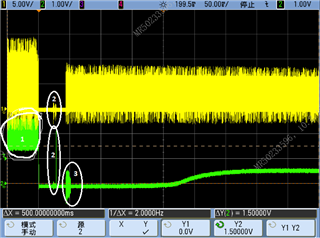

我对此波形和建议有几个问题。

请注意、我为问题和建议的波形编号。

1.使能引脚为什么在变为低电平之前会有超过1V 的高频噪声?

a.)此处不应出现此信息、可能表示您的设计存在布局问题。

b.)数据表提供布局指南和一个示例、供客户参考、并在那里比较布局并根据需要进行调整。

2. 在循环的间隔2中,使能引脚上和输出 A 上有噪声。

答:)我已经看到 VDD 和 VREF 噪声也可能导致 IC 行为异常的问题。

B.)我将重新获取波形、并且也看看 VDD 和 VREF。

c.)如果您遇到过大的 VDD 噪声、通常可以使用低通滤波器来解决该噪声。 与 VDD 电容器和辅助电源串联的电阻为22欧姆 将有助于降低该噪声。

d) VDD 高频旁路电容器需要尽可能靠近 VDD 和接地引脚。

>长线迹充当天线,并将噪声耦合到设计中。

D.)如果 VDD 上有可能耦合到 VREF 的噪声。

c.)为了降低 VREF 噪声、使 VREF 电容器尽可能靠近 VREF 引脚和 IC 接地将有助于降低噪声。

3. 时间间隔3高频噪声低于地电平约600mV。 如果将一个引脚拉至低于接地电压300mV 以上、则可能会导致器件内部隔离出现问题、并导致器件行为异常。

a)要解决此问题、通常可以通过接地端和有效引脚之间的肖特基二极管来解决。 同样、需要尽可能缩短布线长度。

此致、