您好!

以下线程说明 SCG 正在影响断电序列。

根据我的结果、断电时序随负载电流而变化。 当没有负载时、可以通过设置 SCG 来实现所需的断电序列吗?

e2e.ti.com/.../8738.TPS6521905-waveform.pdf

此致、

西井市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

以下线程说明 SCG 正在影响断电序列。

根据我的结果、断电时序随负载电流而变化。 当没有负载时、可以通过设置 SCG 来实现所需的断电序列吗?

e2e.ti.com/.../8738.TPS6521905-waveform.pdf

此致、

西井市

尊敬的 Nishie:

感谢您使用我们的 E2E 论坛。 负载和输出电容是影响断电序列的关键外部因素、因为它们还定义了电源轨放电的速度(或慢)和低于 SCG 阈值的速度。

负载越高、低于 SCG 阈值的电压轨放电越快。 如果在时隙持续时间到期之前输出电压低于 SCG 阈值、PMIC 仍将等待、直到时隙持续时间结束。

如果 在执行下电序列之前更改了寄存器设置"BYPASS_RAILS_DISCHARGED_CHECK"、则时隙之间的时序测量值在加载或空载时相同。 如果您有任何问题或需要其他 信息、请告诉我们。

谢谢。

布伦达

尊敬的 Brenda-San:

感谢您的答复。

通过更改"BYPASS_RAILS_DISCHARGED_CHECK"、我们能够使时序与 GUI 相同。

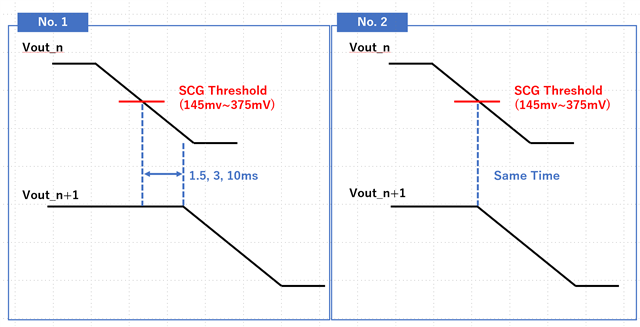

我来问您一个问题。 在轻负载条件下、如果能够识别下一个输出电压(Vout_n+1)在输出电压(Vout_n)达到 SCG 阈值后的时隙(1.5、3、10ms)之间的时序(1)之后开始断电、是否正确?(NO.1)

此致、

西井市

尊敬的 Nishie-san:

在满足这两个条件(之前的电源轨低于 SCG 阈值并且之前的时隙持续时间结束)后、下一个输出电压(Vout_n+1)开始断电。 如果 更改了"BYPASS_RAILS_DISCHARGED_CHECK"、则 PMIC 会在 断电期间忽略 SCG 阈值。 在这种情况下、时隙持续时间将是按顺序断电下一个电源轨的唯一条件。

请注意、断电时隙持续时间是从 输出电压_ n 开始断电、直至 输出电压_n+1 开始断电。

谢谢。

布伦达