主题中讨论的其他器件:TL5209、

下午好!

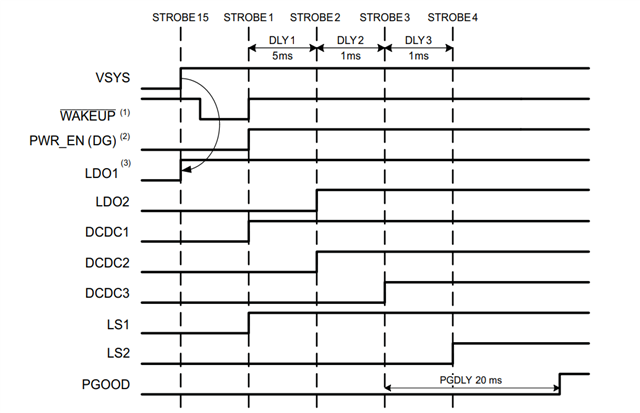

我正在使用 OSD3358-512M-ICB C-SIP 验证 PCBA 设计。 此 SOM 包含一个 TPS65217C PMIC、TL5209 LDO 和一个 AM355x Sitara 处理器。 我的理解是、断电序列应该与上电序列相反。 在很多情况下、我们设计的断电序列与 反向加电序列不匹配。 我希望能够澄清我们是否应该关注这些与预期行为不同的情况。 谢谢!

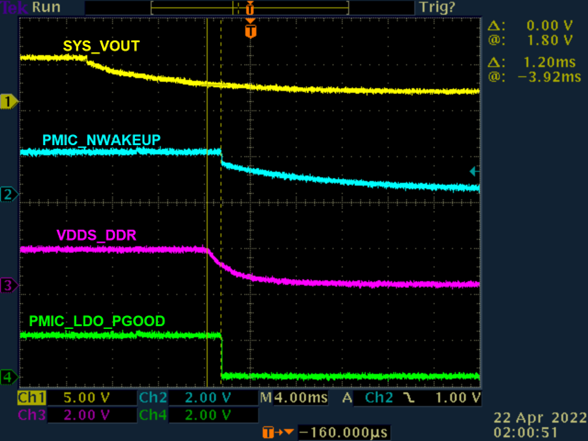

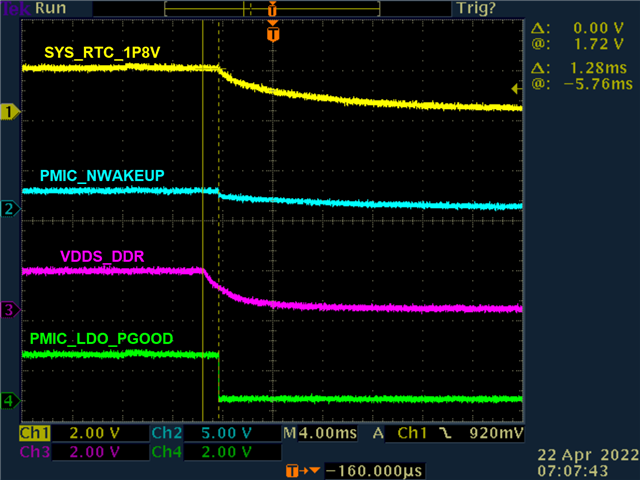

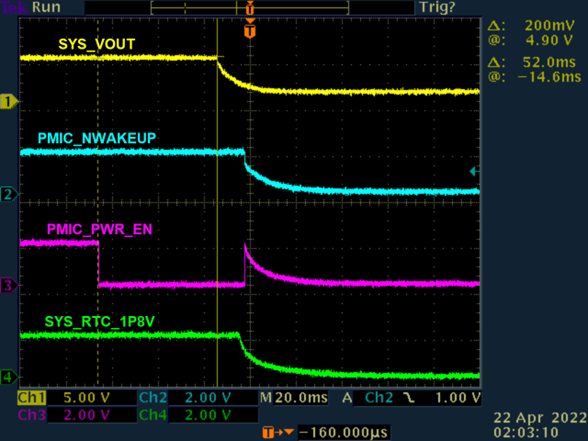

引脚图例:

- PMIC_PGOOD -> TPS56217C PGOOD 引脚

- PMIC_LDO_PGOOD -> TPS56217C LDO_PGOOD 引脚

- PMIC_NWAKEUP -> TPS56217C NWAKEUP 引脚

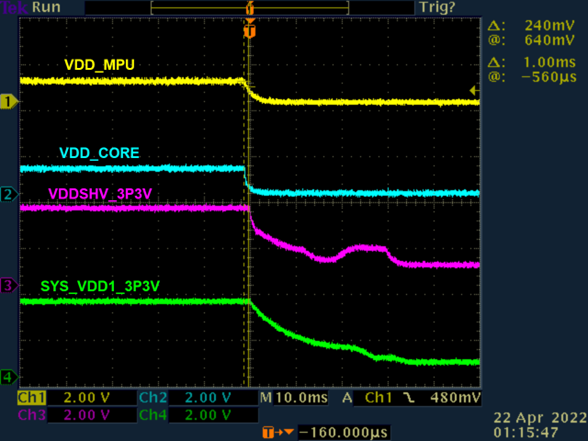

- VDDSHV_3P3V -> TPS56217C LDO4

- SYS_VDD1_3P3V -> TL5209输出

- VDD_CORE -> TPS56217C DCDC3

- VDD_MPU -> TPS56217C DCDC2

注意:我确认了 TPS56217C 的寄存器0x19 - 0x1E 符合 IC 型号的复位状态。

问题:

1. PMIC_PGOOD、PMIC_NWAKEUP 和 PMIC_LDO_PGOOD 压降行为。 在断电期间、这三个信号会在衰减之前被短暂拉至低电平、如预期的那样。 虽然在第一个示波器捕获中并不完全清楚、但所有三个信号的掉出行为都同时发生。 在我们的设计中、这些引脚都连接到 AM355x 处理器上的引脚。 PMIC_PGOOD 连接到 PWRONRSTn 引脚、PMIC_LDO_PGOOD 连接到 RTC_PWRONRSTn 引脚、PMIC_NWAKEUP 连接到 EXT_WAKEUP 引脚。

2.在 VDD_CORE 和 VDD_MPU 开始下降之前,VDDSHV_3P3V 开始下降~3.6ms。 根据反向上电序列、我预计 VDD_CORE 和 VDD_MPU 在 VDDSHV_3P3V 之前大约1ms 开始下降。 在我们的设计中、VDDSHV_3P3V 连接到5/6 VDDSHV 引脚以及外部电压钳位电路。

谢谢!