大家好、

我使用 TPS546D24ARVFR 来满足 Vout=0.85V 和 Iout=120A 的电流要求、采用 x3堆叠配置。 我附上了布局设计和原理图。 请查看布局并提供 feedbacks.e2e.ti.com/.../7774.TPS543B20RVFT.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我使用 TPS546D24ARVFR 来满足 Vout=0.85V 和 Iout=120A 的电流要求、采用 x3堆叠配置。 我附上了布局设计和原理图。 请查看布局并提供 feedbacks.e2e.ti.com/.../7774.TPS543B20RVFT.pdf

尊敬的 Shiftali:

请填写设计计算器并返回给我以加快审核过程。

谢谢。

约瑟夫

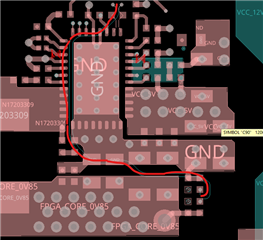

约瑟夫请我帮助他完成这个布局审查。 我再看一下细节、我担心 PGND 和 AGND 之间缺乏单独接地会造成一些旁路问题。

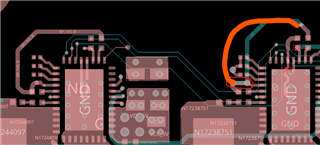

U6将 VSHARE 旁路电容器连接到接地平面、而不是背面连接到引脚37 (AGND)。 如果像在 U7和 U8中那样、将这个接地层返回到顶层的引脚37、而不是连接到 GND 平面并通过散热焊盘向上到 AGND、那就好得多。

每个器件的 VSHARE 旁路电容器的布局略有不同、但最好的布局是 U8、使电容器位于引脚之间、但应移除 C43上方添加的过孔。

U8和 U7使用焊盘中的过孔作为其 Vshare 电容器路由 VSHARE、而 U6有一条布线到过孔。 虽然两种方式都适用、但焊盘中的过孔配置可实现更紧密的布局。 如果焊盘中的过孔增加了成本、U8布局会非常简单地使用一条小的过孔线迹

MSEL1、MSEL2、VSEL 和 ADRSEL 的引脚编程电阻器应连接到 AGND 引脚、而不是通过接地平面。 其他转换器和器件的接地平面中的噪声会影响引脚检测的精度、并产生启动问题。

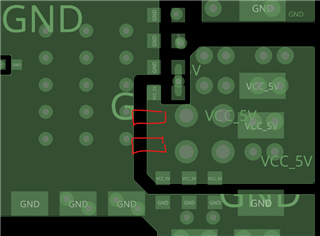

在每个转换器的 PVIN 附近、在 VCC_5V 到 GND 之间似乎有5个0402电容器、但所有这些电容器都远离该器件布线。 我建议在 PVIN 引脚正下方的 VCC_5V 过孔和电源板的 GND 过孔之间移动其中的2个。 这些电容器应介于2.2nF 和10nF 之间。 这些电容器在开关节点的自谐振频率附近具有自谐振、以及足够的 ESR 来进行自阻尼。 (显示了 U6下的示例、但应在所有3个器件上重复该示例)

它也看起来像是 AVIN 旁路到 GND。 AVIN 应旁路至 AGND。 通过散热焊盘将 AVIN 连接到 AGND 可能会引入一些操作问题、尤其是对于 VIN = 5V 的情况。

对于不同相位、相对于输出电容器的过孔位置似乎不同、U6和 U7在焊盘中具有过孔用于接地侧输出电容器、在焊盘中具有 U8过孔用于 VOUT 侧。 U8在电容器附近还有额外的 VOUT 过孔。 我建议所有这些设置都相同。 可放置的靠近电容器的过孔越多、通常性能越好、 但是、我要小心谨慎、不要将几组过孔放置得太近以至于内部接地层无法填充在过孔之间、因为接 地中的"插槽"会显著增加接地阻抗。

U6和 U8在 IC 引脚上连接了输入接地和输出接地、但 U7似乎缺少这一点、我建议将其包含在 U7中

我建议尽可能靠近 VOUT 延长顶部和底部的接地、因为设计规则允许扩大接地面积以进行散热。 如果设计规则允许在封装体下方和封装端子之间存在过孔、这可以显著降低寄生电感并提高瞬态性能和稳定性。

U7和 U8都有2个用于 PB1V5的过孔。 这不需要2个通孔、实际上可以是1个。 此外、U7可能像 U6 IS 一样在顶层进行圆化、以便 VSHARE 可以在从 U8路由到 U7的同一层上从 U7路由到 U6。

它看起来像是 BCX_CLK 由 U6的 VSHARE 短接至接地过孔、除非这是一个盲孔。

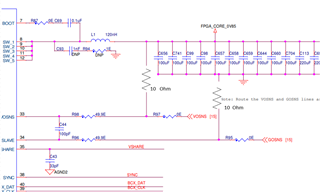

输出覆铜的最右侧离负载最远、可能不是遥感源点的理想位置、也不会在 TPS546D24A 的开关节点侧下方布线返回路径。 我建议将遥感点靠近负载处理器以实现更好的负载调节(负载电流增加时的输出压降)、并使布线远离开关节点以避免噪声耦合。

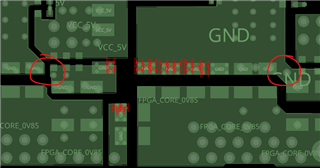

输出覆铜的最右侧(离负载最远)可能不是遥感源点的最佳位置,也不是 TPS546D24A 开关节点侧下方的返回路径布线。 我建议将一个遥感点靠近负载处理器、以实现更好的负载调节(负载电流增加时输出压降)、并使布线远离开关节点以避免噪声耦合。[/引述]当负载为左时、布局在 VOUT 覆铜的右下角具有从 VOUT 到 VOSNS 的连接点、这将导致由于 I×R Drop、输出电压负载线等于检测点和负载之间布线中的电阻 与负载之间的热阻。

将输出电压检测点向左移动、甚至移动到 FPGA 本身、有助于改善负载调节。 如果需要、可以使用相同的电阻将 VOSNS 点连接到 FPGA 周围的多个点、以便对整个 FPGA 区域上的电压求平均值。 每个要平均的点都应连接到具有相同电阻(例如50或10欧姆)的 VOSNS 公共反馈线路。 然后、TPS546D24A 将调节这几个点的平均值。

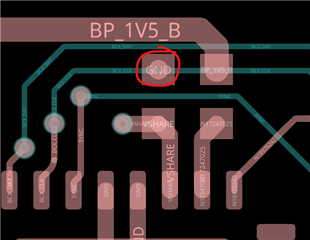

[/quote]2. 此外、C44、R98、R96、R97和 R95是否应放置在 FPGA 或稳压器附近。 请确认[/报价]为了获得最佳性能、请使 C44、R96和 R98靠近 IC、这将最大限度地提高其滤波器对进入反馈环路的噪声的有效性。

R97和 R95应靠近 FPGA 放置、以提供差分感测。

Ω 要在多个点添加平均值计算、请将 R97和 R95增大到10Ω、并增加与 R95和 R97并联的额外10k Ω 电阻以收集到其他检测点。

还可以在 R97当前位置的 FPGA_CORE_0V85与 R97和 R98之间的公共网络之间添加一个电容器、以允许由于 FPGA_CORE_0V85的电源路径中的电感而导致的相位滞后到 FPGA 的检测点。

我已根据您的反馈更新了布局文件。 请查看最新的布局文件并告知我们您的反馈。

谢谢。

什法利

尊敬的 Shiftali:

考虑到负载的压降、VOSNS 的布局仍然不是最佳的。

由于您仍然是直接从器件的输出获取 VOSNS 信号、因此不会考虑从器件输出到 FPGA 的 I x R 压降。

我建议修改原理图、以便 VOSNS 主要来自 FPGA 负载连接:

通过移除器件输出端的 VOSNS 连接、或添加一个10-50Ohm 电阻器、如下面的原理图中所示:

除此之外、我认为新的布局看起来不错。

谢谢。

约瑟夫