您好

请查看我的 PMIC 原理图、因为这对我来说是新设计。

它对我非常有帮助。

此致

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

请查看我的 PMIC 原理图、因为这对我来说是新设计。

它对我非常有帮助。

此致

尊敬的 Ashish:

请将每一项标记为"已使用(或未使用)且已完成"、以填写以下检查清单。 在您分享完成的检查清单后、我再看一下原理图。

此致、

詹姆斯

大家好、James

我已经填充了该表。

请检查此情况、如果需要任何更正、请告诉我。

此致 e2e.ti.com/.../1346.TPS650860-Schematic-Checklist_2C00_-Layout-Checklist.xlsx

阿什什

什尊敬的 Ashish:

我复查了您的原理图。 以下是我的反馈:

如果您有任何进一步的问题、请告诉我。

此致、

詹姆斯

大家好、James

感谢您的答复。

我已经记下了您的观点、并将在我的原理图中更新。

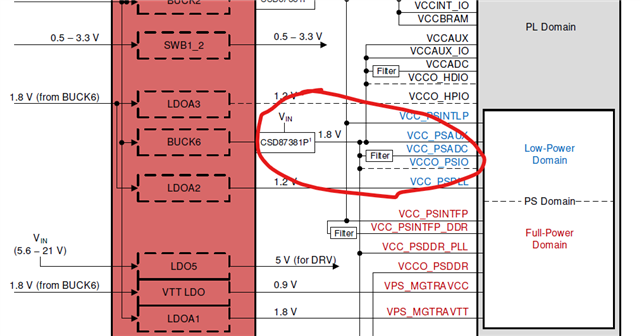

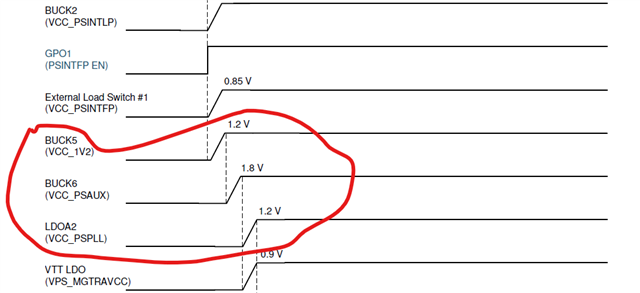

PMIC 数据表中还有1个查询 、因为它与 BUCK6输出相连、所以 VCCO_PSIO 电源在 VCC_PSPLL 之前生成。 您可以在下图中看到、

排序图中、它也来自 LDOA2的 BUCK6控制器之后。 如下图所示。

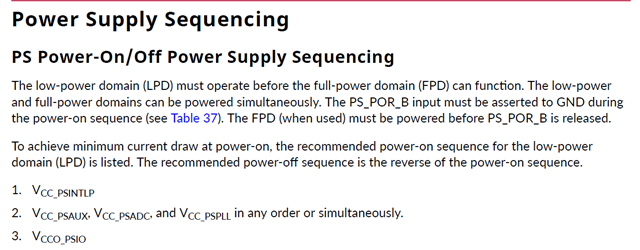

但在 FPGA 数据表中 、您可以在下图中看到建议的定序

请告诉我、hoe 此 PMIC 遵循这项 推荐的时序。

此致

阿什什

什您好、James:

感谢您的答复、

我们有1个关于布局审核的查询、

数据表中提到了对于降压稳压器2信号、DRVH 和 SW 应布线为差分对、但在本例中、电感器放置在距离 PMIC 400mil 范围内、并且我们已按照下图所示对 DRVH 和 SW 进行布线。

如图中所示、 SW 信号采用宽规划布线、而且 DRVH 和 SW 也 未采用差分布线形式。

因此、请告诉我们您对上图中突出显示的信号的看法。

此致

阿什什

什

尊敬的 Ashish:

要进行完整的版式审核、请填写您共享并在此处上传的检查清单的第二部分:

1346.TPS650860原理图检查清单、布局 Checklist.xlsx

此外、请以 Altium 或.brd 文件的形式共享布局、以便我可以详细了解布局。

此致、

詹姆斯