您好!

客户在设计中使用 BQ40Z50、看到过流事件和激活保护(BQ 处的 CHG/DSG 信号变化)的延时为300-400us。 他们预计 tDetect 延迟为160us、但他们看到的却是这两倍。 它们将保护的时间偏移设置为0秒。

这是预期行为吗? 有任何关于如何缩短从事件到保护的时间的建议?

谢谢。

泰勒

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tyler:

提供了一个常见问题解答、其中讨论了硬件和固件保护之间的差异、它可能有助于回答您的问题。 您可以在 BQ40Z50的主页常见问题解答页面上找到相应内容: https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1106884/faq-bq40z50-faqs

数据表中定义了必须考虑的所有硬件保护增加了一个延迟。

此致、

怀亚特·凯勒

Wyatt、

是的、我曾提到"[FAQ]硬件和固件保护之间有什么区别?" 很有帮助。

不过、我希望在这里获得更具体的支持。 根据该常见问题解答、我预计会延迟160us、但客户看到300-400us。 您能帮助我理解它是什么吗?

'当设置 BQ 硬件保护(ASCC、ASCD)上的时序时、已观察到已编程时间与测量时间之间存在300US-500us 的固定时间偏移、表明 BQ 需要触发保护。 即使我们将其编程为0秒以进行保护、在过流事件和激活保护(BQ 处的 CHG/DSG 信号变化)之间也观察到300us-400us 的延迟。 我们预计 tDelay 为160us "

泰勒

请查看所附的.gg 文件和两个范围捕获

e2e.ti.com/.../BQparameters-20230815.gg.csv

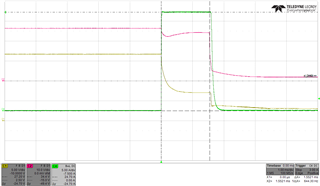

ASCD 24.7A 916延迟

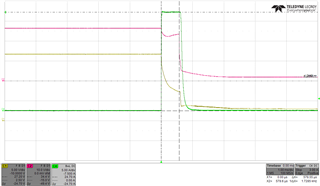

ASCD 24.7A 0delay.png

感谢您的快速回复 Wyatt。 它们的栅极电容为2nF。 对于这个设计、这被认为是大电容还是小电容?

来自客户:

它旨在设置 SCDdx2位。 当 ASCD 阈值1和2设置为0xF4时、ASCD1的预期延迟为1830us、ASCD2的预期延迟为916us (下图)。 由于阈值相同、因此应触发 ASCD2 (较低延迟)。

上限为916 + 916 * 10%+ tDetect = 1168us。 我们测量的值为1552us。

同样、当将 ASCD 阈值1和2设置为0x04 (预期~瞬时触发)时、我们测量的延迟为578us (再次高于0 + tDetect = 160us)。

对于触发延迟增加的原因、您有什么见解吗?

泰勒