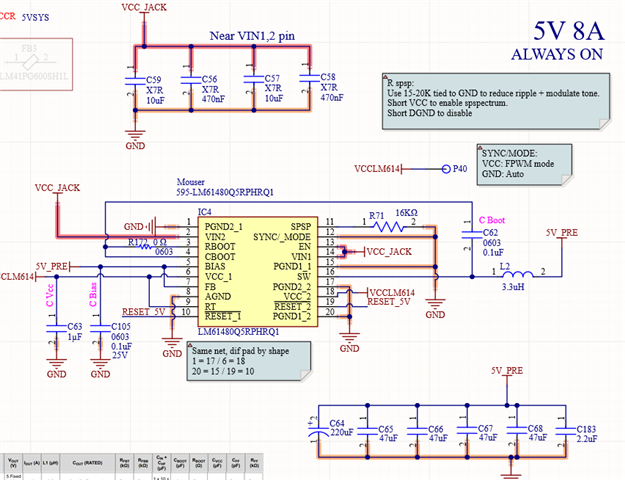

大家好、我正在使用[LM61480Q5RPHRQ1、VoutFIX = 5V、Iout = 8A]。 我在布局指南中看到这一点"使 PCB 顶层和底层具有2盎司铜且不小于1盎司"。

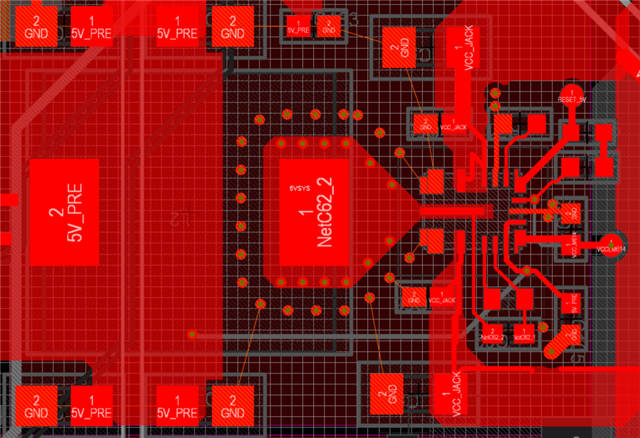

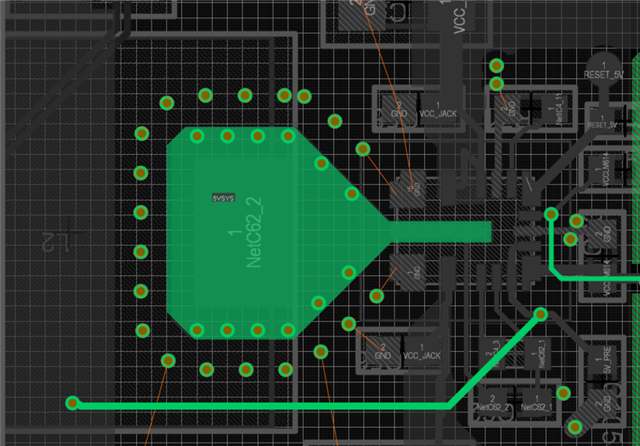

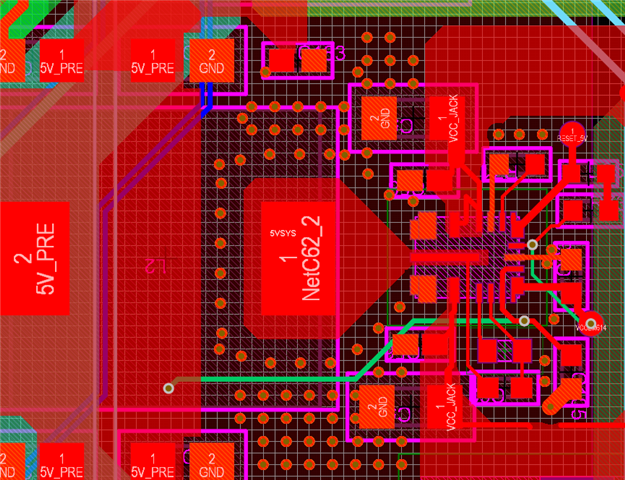

我使用的是6层 PCB、每层均为1盎司。 厚度。 如果顶层不是2oz、将出现任何问题。 是否可以使用另一层来增加覆铜? (特别是 SW 节点、可以使用通向另一层的通孔向该节点添加更多的铜。是否有好主意?)。

第2层、5层是 GND 平面。 稍后将向左侧空间浇注 GND 过孔。

PS。 如果有任何我可能没有意识到的糟糕设计、请告诉我。