Other Parts Discussed in Thread: TPS62933

大家好、我的目标是设计一个采用 TPS62933的降压电路。 输入=24VDC、输出=10V 3A。

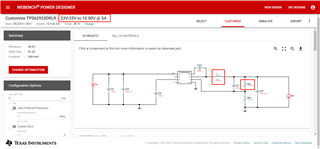

设计 :使用 Wenech 设计电路

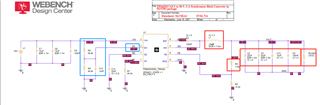

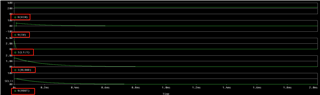

仿真值 :使用 PSpice for TI + TPS62933 PSpice 瞬态模型 验证上述 电路。 根据 webench 设计、我对 示例 PSpice 电路进行了以下修改(参见红色框)。 仿真结果如下所示。

问题

1) 为什么 V (SW)刻度下降? 此信号应为0或24V 开关信号。 因此、I (RLOAD)和 V (VOUT)不是10V 3A。

2) 请参阅蓝色框、为什么使用两个49.9k Ω 分压器的24V 电压使 EN 引脚= 5V? 电阻电压分压器应为12V。

3) 在输出负载处、为什么仿真结果递减到0V、但标签仍然显示5V?

非常感谢