我们终于不久前再对该电路进行工作了—

延迟不起作用-输出是同时进行的? VO1>VO2应为~40ms... 不是。

此外- VO3不是从 VGH 引脚输出。 我们在 CPI 上有15V 电压(关闭前)

CTRL 为高电平、VI 为2.5V

DRVP 达到15V

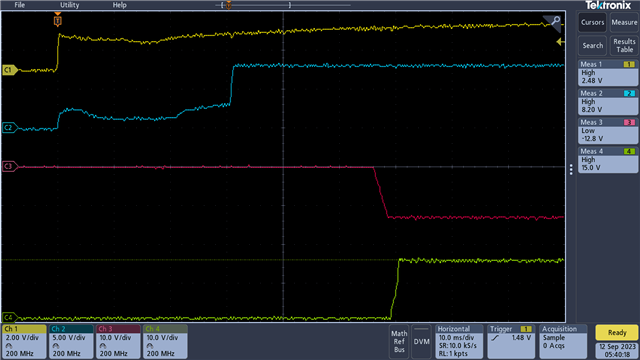

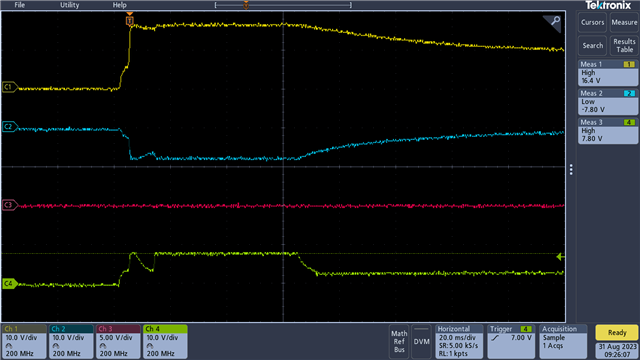

下面是上电的示波器捕获、其中显示了启动和关闭电压;

CH1 (黄色)为 CPI

CH2 (蓝色)是 VGL

CH3 (红色)是 VGH

CH4 (绿色)为 AVDD

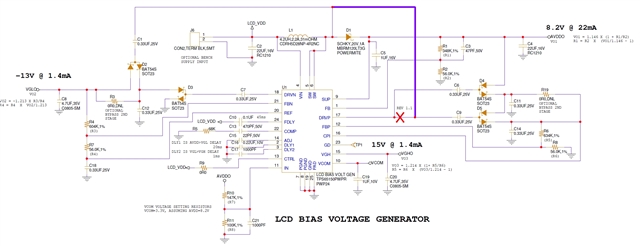

请查看我的原理图并确认设计。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们终于不久前再对该电路进行工作了—

延迟不起作用-输出是同时进行的? VO1>VO2应为~40ms... 不是。

此外- VO3不是从 VGH 引脚输出。 我们在 CPI 上有15V 电压(关闭前)

CTRL 为高电平、VI 为2.5V

DRVP 达到15V

下面是上电的示波器捕获、其中显示了启动和关闭电压;

CH1 (黄色)为 CPI

CH2 (蓝色)是 VGL

CH3 (红色)是 VGH

CH4 (绿色)为 AVDD

请查看我的原理图并确认设计。

C1未使用

C2为 AVDD (设置为8.2V)

C3是 VGL (设置为-13V)

C4为 VGH (设置为15V)

为什么在进入所需的-13V 之前、VGL 会立即降至~7.5V 并持续~45ms?

我们对2个电路板进行了测试、结果相同。 我们有第三个电路板尚未通电。

所需的时间/延迟如下:

FDLY 在~45ms 的延迟时间内具有0.1uf (移除并连接至 VIN 以获取最新结果)

DLY1具有0.22uf 并持续~20ms 的延迟 AVDD 至 VGL

DLY2具有1000pF 的~1ms 延迟 VGL 到 VGH

在所需时序中、这些电容器值是否正确?

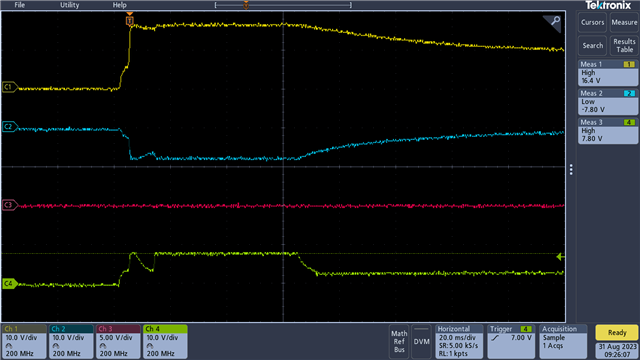

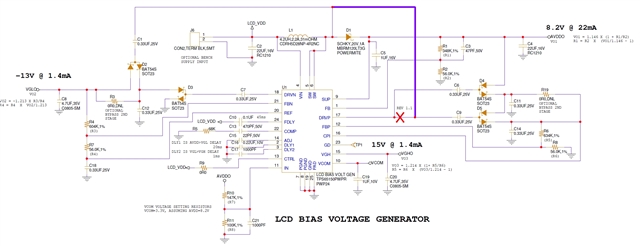

让一切正常工作!

修复;

1.必须交换 FDLLY<>DLY1的电容器、故障延迟似乎短于 VGL 启动、因此 IC 关闭。 不知道哪里的计算出错了....

2、分别更改了 VGL 和 VGH 第二级由 DRVN 和 DRVP 驱动-这样就摆脱了 VGL 上的步骤。 VGH 第二级最初由 DRVP 驱动、因此使用 DRVP。

电流波形;

C1 = VIN (2.5V)、C2 = AVDD (8.2V)、C3 = VGL (-13V)、C4 = VGH (15V)