您好!

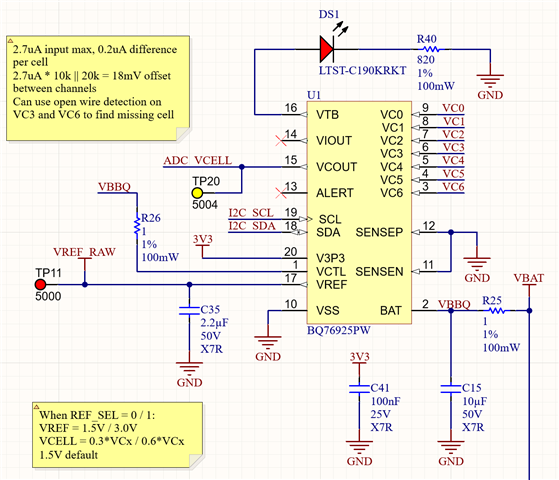

我有一个 BQ76925、具有外部3.3V 调节。 VCTL 如数据表中所示连接到 VBAT、还有一个单独的3.3V LDO、其输出连接到 V3P3。 当我通过 I2C 开启 VREF 时、它会上升到4.0V、这对我的微控制器来说是很危险的。 这可能是什么原因造成的? 到目前为止、我在2个板上看到了该问题。 我的原理图如下所示(请注意、R40替换为1.5k Ω、以保持在数据表中的1mA 限制范围内):

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我有一个 BQ76925、具有外部3.3V 调节。 VCTL 如数据表中所示连接到 VBAT、还有一个单独的3.3V LDO、其输出连接到 V3P3。 当我通过 I2C 开启 VREF 时、它会上升到4.0V、这对我的微控制器来说是很危险的。 这可能是什么原因造成的? 到目前为止、我在2个板上看到了该问题。 我的原理图如下所示(请注意、R40替换为1.5k Ω、以保持在数据表中的1mA 限制范围内):

Anand、您好!

我建议 从 V3P3引脚上移除外部3.3V LDO 输出、并添加 4.7uF 旁路电容器。

请参阅此过往 E2E 的 V3P3与 VCTL 连接: (+) BQ76925:bq76925:外部稳压器(未使用的 V3P3)-电源管理论坛-电源管理- TI E2E 支持论坛。

另请参阅入门应用手册中的第6节、详细了解 LDO 稳压器: bq76925入门(修订版 B)。

此致!

安德里亚

Anand、您好!

感谢您的澄清。 我误解为您遇到了 V3P3问题。 尽管您应该在 V3P3上使用一个4.7uF 的电容器、但 VREF 和 V3P3是不同的内部电路。 V3P3引脚是通常用于为 MCU 供电的输出、因此不建议将其用作外部 LDO 输出的输入。

对于 VREF 引脚输出、您是否看到稳定的4.1V 输出、还是线路上有噪声导致电压尖峰? 此外、VREF 引脚通常连接一个1uF 电容器。 您能否发送完整的原理图以便我可以查看所有连接、包括 GND 路径?

此致!

安德里亚

Vref 输出稳定在4V 左右、但在我将电源电压降至6V 以下时确实会出现压降/欠压。 电压曲线相当一致、我没有看到任何尖峰、它高达4V、并一直保持在那里、直到我禁用 VREF 位。

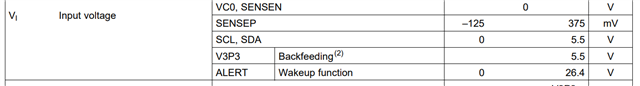

请注意、 数据表中明确允许反馈 V3P3 (最高5.5V)。 我已为其供电以实现冗余。

Vref 的电容器为2.2uF、因为数据表应用示例建议最小电容为1uF。 我无法发送完整的原理图、但我发送的片段包含了与功率相关的所有内容。 GND 在整个 PCB 上浇注大量缝合过孔。 可能是 Vref 具有过大的电容器、导致上电时出现过冲、然后发生永久损坏? 但如果故障模式是故障模式、我希望数据表中会提供一些文档。

Anand、您好!

我很抱歉——我看到 V3P3上的电容缺失了,以为反馈是一个疏忽。 您是正确的,这是允许的回送。

不过请注意、 如果提供的电压高于内部稳压器、则内部稳压器不提供 电流、但如果提供的电压低于内部稳压器、则内部稳压器将尝试提供电流来提高电压。 建议在 VCTL 引脚和 BAT 引脚之间连接一个高阻值上拉电阻器。 这应将内部稳压器提供的电流限制在非常低的水平。

就有关 VREF 上的电容器尺寸的理论而言、我认为2.2uF 不应像您描述的那样损坏器件、尤其是因为1uF 是建议的最小值。 您是否已 通过 示波器观察到 VREF 输出?

GND 基准上的噪声可能会干扰器件。 如果您能够接收任何系统噪声、那么您可以相应地选择一个电容器值、以便根据其频率将其滤除。 此外、 如果 REF_SEL 设置为0、您是否在 VREF 引脚上看到输出?

其他注意事项:

此致!

安德里亚

好的、谢谢、听起来好像还有几个不同的方面、所以我可能需要在重新插入电路板后才能找到解决方案。 我 现在无法用我的工具焊接10k 来提醒我、因此侵入是合理的。

当 REF_SEL 为0时、我看到~50mV 的输出(基本为0)。 在示波器上探测 Vref 会显示恒定的~4V 电压、而没有明显噪声。 我目前没有任何切换或在电路板上产生 EMI、因此我犹豫是否认为它是布局问题。