您好!

LM5157的过流保护阈值是多少?

内部 MOSFET 的最大耐受电压是多少?

此致、

兰尼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Rannie。

在这个问题中、我也会坚持使用数据表规格。

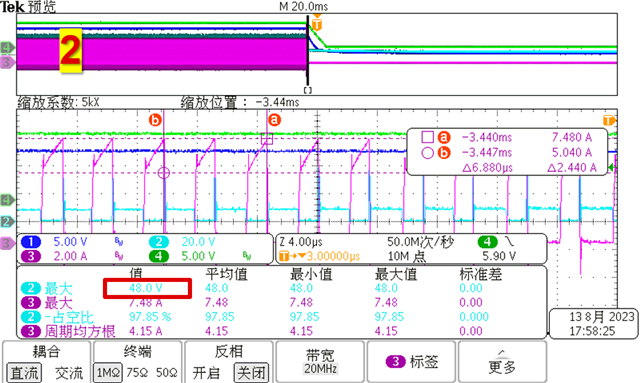

建议的最大 VDS 电压为48V、而50V 为绝对最大额定值。

我会考虑这些短期和长期的限制。

由于有额外的内部裕度、因此如果出现51V 的短电压尖峰、我不会认为器件会直接损坏、

但 TI 无法正式保证器件正常运行、即使在短时间内超出这些限制也是如此。

我假设波形的蓝色信号是开关节点?

如果只有几个略高于50V 的尖峰、则损坏器件的风险较低、但波形看起来绝对最大额定值每隔几个开关周期就超过一次、甚至还有尖峰超过70V。 这实际上可能是一个问题。

此致、

尼克拉斯

您好、Niklas、

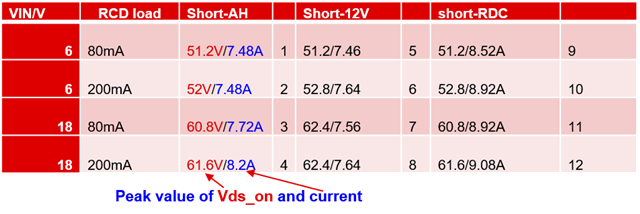

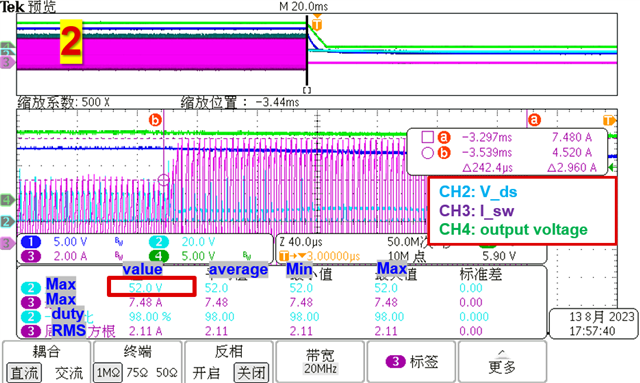

抱歉上面的波形中没有标注详细信息、下面是客户的设计和波形图。

Inovance 使用 LM5157设计具有4个隔离式输出的反激式转换器: 18.2V *3 ( 啊 、BH 和 CH、它们是相同的) 12V *1 和1个一次侧反馈绕组( RDC )。

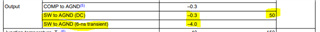

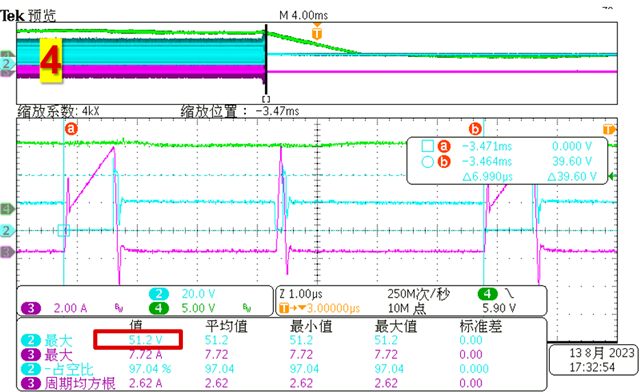

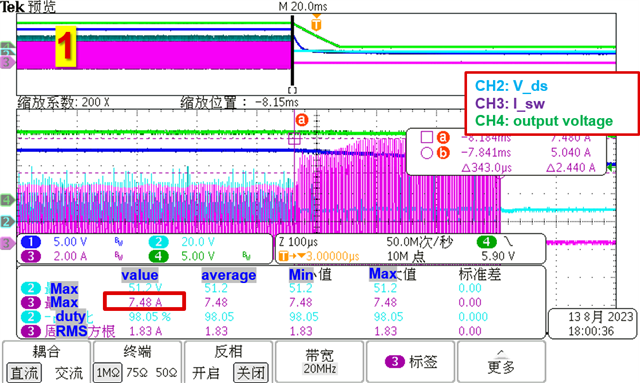

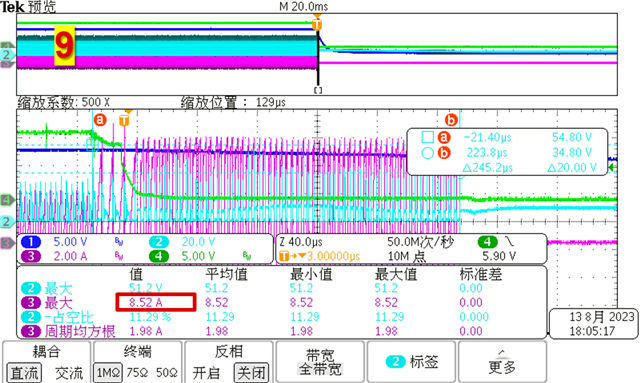

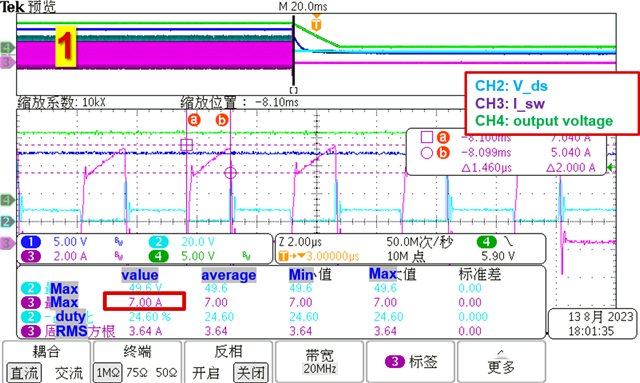

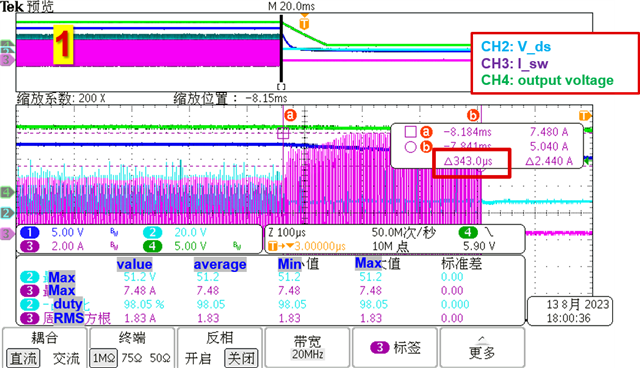

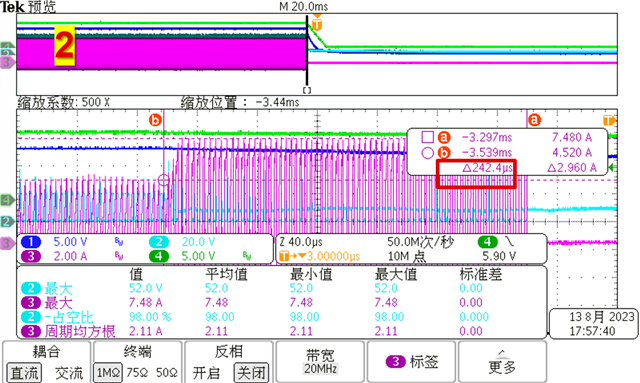

他们在不同条件下对 LM5157的 OCP 进行了测试、结果如下所示:

有 3个问题需要您的帮助以解决或向客户解释:

1. 为什么 Vds (on)上出现电压尖峰、MOS 上出现电流尖峰 变大 之后 VIN 增大 在相同的负载下、例如、Vin 从8V 到16V、VDS_ON 从52V 到61.6V (vs. 2和4)(众所周知)、MOS 上的电压与输出电压有关。

2. 为什么要这样做 电流峰值增加 之后 将 RDC 负载短接 (初级反馈绕组)相比、隔离式绕组(12V 和 AH)是否短路? (对比1和9、2和10、3和11、4和12)

3、 为什么负载越重,响应速度越快? (与1和2比较)

此致、

兰尼

您好、Rannie。

感谢您的更新和波形。

以下是我对这些问题的评论:

1、FET 的 Vds 电压取决于输出电压 和 输入电压。 这意味着电压峰值与输入电压一起上升。 为了更好地说明这一点、我建议查看我们的功率级设计器工具:

https://www.ti.com/tool/POWERSTAGE-DESIGNER

选择反激式拓扑后、您可以双击原理图中的 FET、查看电压值随输入电压的变化而上升和下降。

2.很难理解为什么使用 RDC 绕组时的电流比使用输出绕组时的电流更高。 可能的因素是耦合系数、绕组比和电感的差异。 为了确认这一点、我需要了解有关变压器的更多详细信息。

3.您是说在发生短路事件之前负载更高时、器件进入断续模式的速度会更快?

根据数据表、在触发断续模式之前、器件会计数64个电流限制周期。

我假设由于这种反激式设计、电感器电流需要一些额外的周期才能在短路事件后斜升并达到 OCP 阈值。 如果由于负载较高、电感器电流已经处于较高的起点、则 OCP 阈值的裕度较小、因此达到更快。

还有一条注释、

查看变压器原理图时、会发现初级侧电源绕组的连接方向错误。 电源将需要从 KL30_P2 (连接到电源)到 KL30_P1 (连接到 FET 和 GND)以使反激式器件正常运行。

此致、

尼克拉斯