主题中讨论的其他器件:CSD87350Q5D、

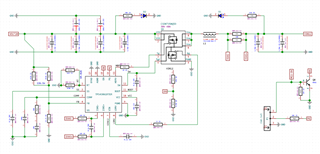

我将使用 CSD87350Q5D 电源块的 MOS、设计效率高达96%的12V 21.8A 输入20V12.5A 输出升压电源。

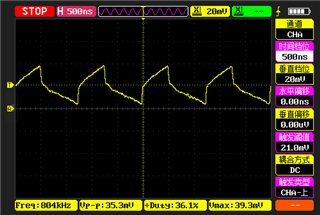

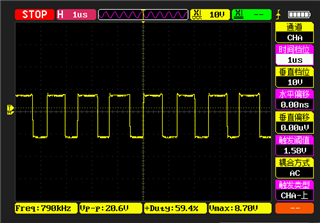

设计开关频率约为820kHz (实际值790kHz)、电流限制为2MR (D=40%时为35.6A)、文章末尾给出了详细的计算参数。

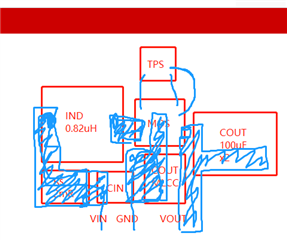

PCB 布局↓μ F、所有高电流迹线都使用1x1mm 铜带来扩展载流能力。

输出电容为:

已计算并实际使用的环路补偿参数、

R_COMP=27.17k (30k)

c_comp=9.10n (10n)

c_hf=30.24p (33p)

这些值通过了 Webench 功率检查和仿真。

然而、该环路补偿参数的实际测试结果是发生过流保护。

|

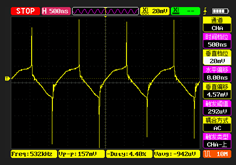

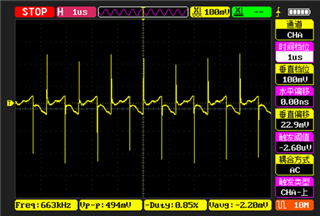

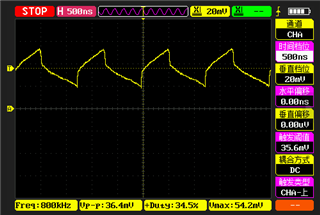

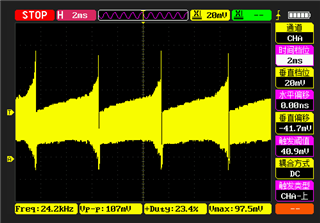

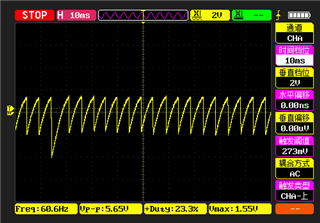

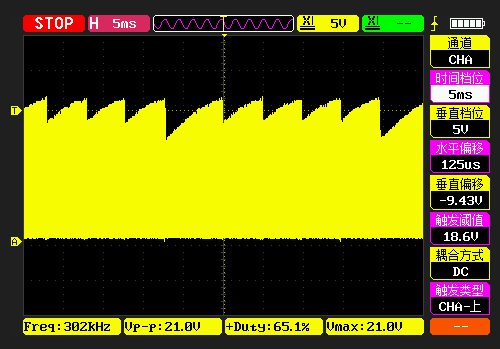

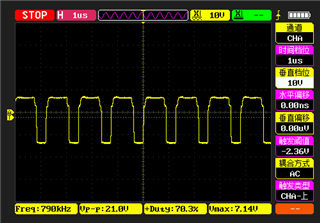

2MR 电流检测电阻上出现107mV 峰值(下图1)、 SS 电容器上出现了再充电(下面的图2)、 和 SW 长时间波形(下面的图3) |

|

|

HS 控制波形、LS 控制波形和 SW 波形 都是正常的、但触发过流保护、 但是、由于电流保护引起的欠压、占空比会发生变化。 |

|

如果将 COMP 值更改为:

R_COMP=30k

c_hf=10n

C_COMP=33p

通过交换 C_HF 和 C_COMP、电源可以稳定地输出20V10A。

但是、Webench 警告称该补偿值未通过检查、表明相位裕度过低。

|

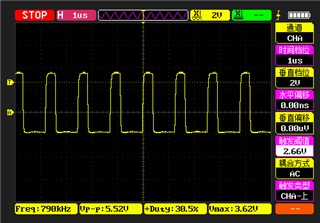

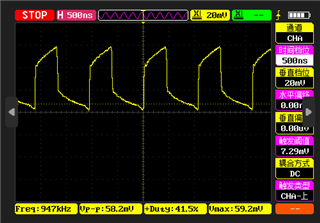

这是另一个配对 C_COMP 和 C_HF 电流检测波形的测试板。 开关频率为940k、 在理论计算下使用环路补偿参数时、也会出现上述问题。 2MR 电流检测电阻器仅有58mV 的峰值(图1) |

|

我想问是什么原因造成了这种情况? 以及如何解决该问题。

当使用接近理论计算值的 COMP 组件参数时、检测电流为100mV 时、为什么峰值电流约为50A?

此外、我正在使用一组理论上无法稳定的值、但我可以保持稳定的10A 输出呢?

之前我还设计了一个针对 TPS43061的测试板。

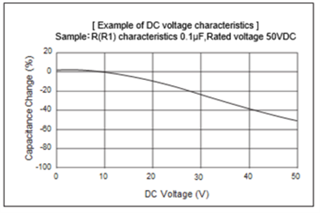

它使用了 CKG57NX7R1H476M500JJ 双层电容器、

两个并联的电容器可得到一个大小为66uF 5MR 左右的低 ESR 输出电容器、以及一个额外的330uF 固态电容器来提供输出电流。

使用计算得出的 COMP 补偿参数、可在不触发过流保护的情况下使输出保持稳定。

C_OUT_LIST = [

[11.6 * uF, 3 * mR],

[11.6 * uF, 3 * mR],

[3.3 * uF, 3 * mR],

[5 * uF, 20 * mR],

[100 * uF, 35 * mR],

[100 * uF, 35 * mR],

]

===== DESIGN =====

V IN = 12.00V [11.80V~12.30V]

I IN = 21.72A

POUT = 20V 12A

EMAX = 96.5%(-8.84W)

===== BOOST =====

Duty = 40% [38%~41%]

SW = 823kHz MAX:2357kHz

RT = 69.82kΩ

===== IND =====

L = 0.80uH(0.82)

I = 21.21A rms:21.31A peak:24.88A

RS = 2.00mΩ(<2.11mR) 2.59W

CURRENT LIMIT = 35.65A(>33.75A)

IND TD = 1.903W

===== MOS =====

I gd = 23.39mA

P COND = HS:1.339W LS:0.392W

P LOSS = SW:0.376W DT:2.238W

TDP = 4.344W

===== CAP =====

V IN RIPPLE = 37mV(60) 0.3%

C IN = 30uF(7.39)

V OUT RIPPLE = 26mV(200) 0.1%

C OUT = 232uF(31.13)

C OUT ESR = 0.90mΩ (6xCap)

C OUT I RIPPLE = 10.60 A

===== CONFIG =====

R FB HS = 226.50kΩ

R FB LS = 14.70kΩ

C BOOT MIN = 0.034uF

C SS MIN = 0.100uF

R UVLO HS = 47.00kΩ

R UVLO LS = 5.42kΩ

UVLO DIS:10.79V EN:11.61V

===== COMP =====

R COMP = 27.17kΩ

C COMP = 9.10nF

C HF = 30.24pF

===== Freq =====

Adc = 17.70V/V

f_Pmod = 0.43kHz

f_Zmod = 0.76MHz

f_RHPZ = 110.70kHz

f_co1 = 27.68kHz

f_co2 = 164.70kHz

f_co = 27.68kHz