主题中讨论的其他器件:BQ76200、INA180、 BQSTUDIO

大家好、我正在使用 BQ7695201 IC 开发一款 BMS 产品、我已经为 IC 上电、并通过 SPI 与板上的主机 MCU 进行通信。

我打算使用 BQ76952来替代较早 BMS 产品上 Linear 的 LTC6803。 在该产品中、主机 MCU 控制所有电池平衡、电流监控和 FET 控制、因此我希望也可以对 BQ76952执行相同的操作、因此可以将其用作电池电压监控器、平衡器(与 LTC6803配合使用)、充电电流监控器(与 INA180配合使用) 和高侧 FET 控制器(通过 BQ76200实现)。 如果我可以使用 BQ76952来完成所有这些操作、它将极大地简化 BOM 和空间要求。 我不打算使用自动保护功能、而是使用主机 MCU 轮询数据、然后通过 BQ76952手动控制 FET 和平衡、但我需要首先解决这个问题。

我在使 DSG FET 保持开启时遇到问题。

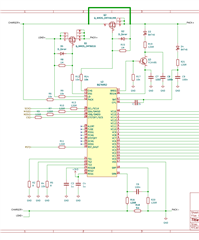

这是 BQ76952的原理图。

TS1和 TS3电阻器以及充电 FET Q2当前未组装。

我在 LOAD+/LOAD-路径中具有一个带前置电阻器的 LED、以便轻松查看 DSG FET 何时启用。

我将从工作台电源为 PACK+和 PACK-提供15V 电压。

下面是我的启动脚本的简短摘要:

Starting procedure //enter CFG_UPDATE 0x0090 //REG0 config 0x9237, 0x01, enable BREG //REGREG12 config 0x9236, 0x0D, set REG1 to 3V3 and enable //SPI config 0x923C, 0x60, set SPI to use REG1 voltage //FET options 0x9308, 0x0C, set mosfet configuration to parallel mode (disable body diode protection) //DSG FET A protections options 0x9269, 0x00, disable all protections //DSG FET B protections options 0x926A, 0x00, disable all protections //DSG FET C protections options 0x926B, 0x00, disable all protections //enabled protections A protections options 0x9261, 0x00, disable all protections //enabled protections B protections options 0x9262, 0x00, disable all protections //enabled protections C protections options 0x9263, 0x00, disable all protections //protection configuration options 0x925F, 0x00, 0x00, disable all protection //TS1 config 0x92FD, 0x00, not used and not used for any protection //TS3 config 0x92FF, 0x00, not used and not used for any protection //exit CFG_UPDATE 0x0092

当我退出 CFG_UPDATE 模式时、DSG FET 会在短时间(~1s)内被激活、我想我看到其他人报告了相同的行为、这似乎是标称值。

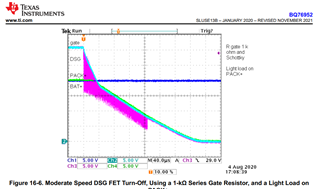

如果我在慢环路中重复调用 DSGTEST 0x0020、DSG FET 后面负载路径上的 LED 会闪烁一次(短暂闪烁)并熄灭。 它不会持续运行。

如果我不是 DSGTEST、则调用 FET_EN (0x0022)以更改为正常工作模式、然后在循环中调用 ALL_FETS_ON (0x0096)、也不会发生任何情况。

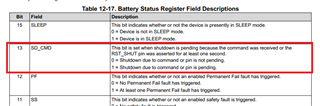

我首先怀疑 DSG FET 被一些集成保护功能禁用、但我尝试禁用针对这种功能的所有可能的配置标志。 此行为是否存在任何其他可能的固件方面的原因、或者这更可能是硬件问题?

我已经测得 CP1电荷泵电容器被充电至预期的11V、因此它看起来正常运行。

我还读取了所有警报、故障和 PF 寄存器、但它们都不会报告任何故障、DSG FET 只是没有保持启用状态。