主题中讨论的其他器件: BQSTUDIO

您好!

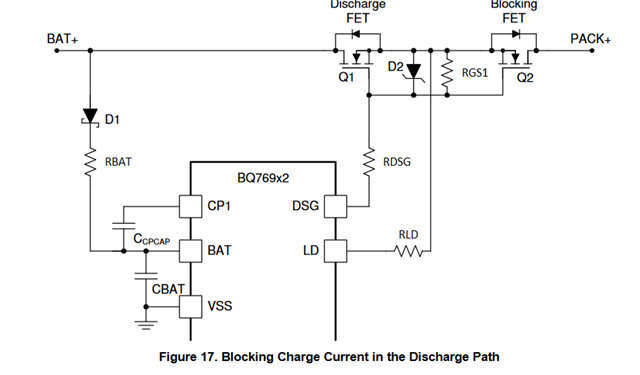

我们将在并联 FET 配置中使用 BQ76952 (我们将 Settings:FET:FET Options - SFET 设置为0)、我们会注意到 CFETOFF 和 DFETOFF 引脚出现异常行为。 我们通过微控制器来控制这两个引脚、并且这两个引脚均配置为交替功能(Settings:Configuration:CFETOFF/DFETOFF Pin Config 都设置为0x2)。 单独来看、这两个引脚都能正常工作。 如果只有一个引脚为高电平、则相应的 FET 确实会关闭。 但是、在我们的固件逻辑中、当在充电或放电模式之间切换时、所有充电/放电电路都关闭、然后再启用另一侧、因此会在一个短暂的时间内、CFETOFF 和 DFETOFF 都处于高电平。 但是、情况似乎不是这样、当 CFETOFF 和 DFETOFF 都为高电平时、放电 FET 似乎保持导通。 我知道、在串联配置中、为了保护放电 FET、这是预期行为、但为什么在并联模式下会发生这种情况?