我们使用的是 TPS7A2433DBVR

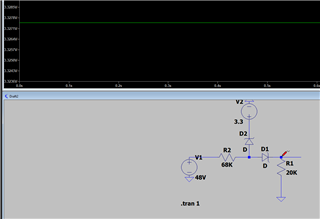

3.3V 固定电压稳压器。 我们有大约 48V 的电压、通过电阻分压器耦合到大约10V (R1 = 68k、R2=20k)的 TPS7A2433DBVR 输出端(由5V 电源驱动)。

V2是 TPS7A2433DBVR

输出端的有效功率限制将电压拉低至10V 至3.3V。 其影响是微控制器数字输入的电压不超过允许的3.3V。

我们的问题是:这是一个常规的使用吗? 当永久使用下拉机构时、可能会出现什么问题?

提前感谢!

汉斯-乔格·齐默尔曼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们使用的是 TPS7A2433DBVR

3.3V 固定电压稳压器。 我们有大约 48V 的电压、通过电阻分压器耦合到大约10V (R1 = 68k、R2=20k)的 TPS7A2433DBVR 输出端(由5V 电源驱动)。

V2是 TPS7A2433DBVR

输出端的有效功率限制将电压拉低至10V 至3.3V。 其影响是微控制器数字输入的电压不超过允许的3.3V。

我们的问题是:这是一个常规的使用吗? 当永久使用下拉机构时、可能会出现什么问题?

提前感谢!

汉斯-乔格·齐默尔曼

尊敬的 Hans-Joerg:

我们有大约 48伏的电压通过电阻分压器耦合到大约10伏(R1 = 68k、R2=20k)到 TPS7A2433DBVR 的输出端、由5V 电源驱动。 [/报价]这对我来说毫无意义。 您说用5V 电源驱动是什么意思?

[/quote]Unknown 说:输出的有效功率限制将电压拉低至大约10V 到3.3V。 其影响是微控制器数字输入的电压不超过允许的3.3V。 [/报价]您是否认为3.3V LDO 输出会将10V 下拉至3.3V?

我不确定我是否理解这个下拉电阻器的原理。 此电路的目的是什么? 您是否有可以分享的实际原理图以便我可以更清楚地看到您所描述的内容?

谢谢。

尼克

您好、Nick。

感谢你的评分

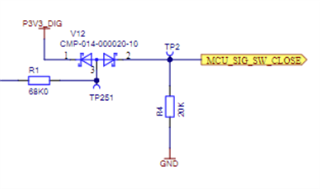

原理图如下所示:

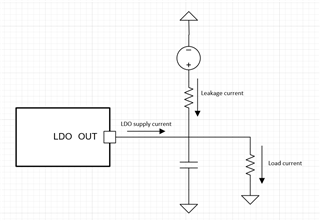

48V 通过外部继电器切换至 X1C、作为闭合继电器的信号。 然后、该48V 电压通过 R1 (用于信号连接器)提供 给二极管耦合、二极管耦合 在一侧由 TPS7A2433DBVR 输出驱动至3.3V (P3V3_DIG)、而在另一侧提供给 MCU 数字输入"MCU_SIG_SW_CLOSE"。 原因可能是48V 信号在30V 和48V 之间变化、因此给数字输入的限制带来了问题。

通过这种方式,如果 TPS 下拉至3.3 V,我们实现了两个稳定点: Relais 打开: 0V; Relais 关闭: 3.3V。

TPS7A2433DBVR 的输入端由5V 输入驱动。

这´s 它目前的工作方式。

此致、感谢您的帮助

汉斯-约尔格

尊敬的 Hans-Joerg:

谢谢你的解释、我想现在就明白了。

LDO"下拉"电源轨的问题是 LDO 本身无法向其输出端灌入电流、 因此、它唯一能够做到这一点的方法是 LDO 上的负载大于从48V 到3.3V 网络的泄漏电流、这样48V 电压就能提供部分负载、而 LDO 则能提供剩余负载并保持稳压。 根据您在此处展示的配置、 LDO 上几 mA 的负载就足够了。 此负载需要始终存在、否则3.3V 输出将为其提供净电流、并将充电至更高的电压。

此致、

尼克

您好、Nick。

再次感谢您的快速响应!

我无法看到您谈到的电流损耗。 在这里、您可以看到原理图中涉及 P3V3_DIG 的所有部分。

——

我发现在 Tps7a24的数据表中、我们使用了一个介绍有源过冲保护的段落:

"

7.3.6有源过冲下拉电路

该器件具有连接至 VOUT 的下拉电路。 此电路为100-μA 灌电流电路、与

由 VEN 控制的5.5-kΩ 电阻。 当 VEN 低于 VEN (LOW)时、下拉电路被禁用并且 LDO

输出处于高阻抗模式。

如果在 VEN≥VEN (LOW)时输出电压比标称电压高2%以上、则下拉电路将关闭

打开、输出被下拉、直到输出电压在标称电压的2%以内。 此功能

有助于减少瞬态响应期间的过冲。

TPS7A24

SBVS386E–2019年8月–2022年9月修订 www.ti.com

12

„

我希望您可以帮助我了解在这里工作的机制、这些机制实际上为 MCU 提供3.3伏的输入。

我认为针对效果使用了这个过冲机制。 我最重要的问题是:

这是 TPS 允许使用的用例吗? 在这种情况下、必须要寻找什么?

这将是伟大的,如果你能给我一些理解在这!!!

此致

汉斯-约尔格

尊敬的 Hans-Joerg:

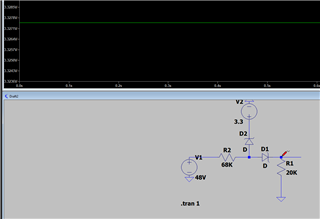

请参见下图。 我的意思是、如果进入 LDO 输出的泄漏电流大于负载电流、则 LDO 电源电流变为零、并且在输出端有净电流、从而导致电荷构建和输出电压上升。

我没意识到这是少数具有这种有源输出下拉电路的器件之一。 我认为情况仍然是一样的、因为有源输出放电电路仅在输出电压比标称输出电压高大约2%时才会开启、因此对于正常使用而言、您可能希望避免这个用例。 换句话说、如果您仅依赖此有源下拉来灌入泄漏电流、则输出将始终比标称值高2%。 如果可以确保负载电流始终大于泄漏电流(小于1mA)、则无需使用有源放电电路。

此致、

尼克

您好、Nick。

感谢您的解释、二极管 V12和 V13仍然有问题。 如果您看一下方向、可以看到、如果没有48V 电压、则3.3V 输出不会到达负载。

二极管耦合中的电压值为:

引脚1:3302 V;最后一位数字悬空

引脚2:0 V

引脚3:0V

因此、TSP 通过二极管

当48V 连接到输出时、测量以下值:

引脚1:3302V;最后一位悬空

PIN2:3323V

引脚3:3606 V

我可以看到二极管上的压降、这意味着电流从3流向1。 下降是(3606–3302)= 0304 V,这意味着有一个从48V 电源流入 TSP 的输出。

此外、电压从3降至2。 压降为(3606–3323)= 0283V、这意味着有一个从48V 电源到 MCU 测量的电流。

这些二极管为肖特基二极管。

所以、我认为激活有源机制的方法是将48V 过孔二极管放在 TSP 输出端、从而得到这些值。

您能这么看吗? 还是我完全错了?

此致

汉斯-约尔格

尊敬的 Hans-Joerg:

是否所有其他连接都是简单的上拉? 这些是否是与 P3V3_DIG 网络的唯一其他连接?

我不完全理解您对二极管的评论、因为与 P3V3_DIG 的所有其他连接都是负载到 LDO。 如果激活了有源下拉功能、则 LDO 输出将比预期高约2%、但在两种情况下都正好为3.3V。 所以我认为所发生的情况是、GPIO 引脚的负载电流(或者如果有更多未显示的电流、则连接到 P3V3_DIG 的任何其他电流) 足以防止 LDO 输出上升、从而使通过 V12的电流基本上为这些连接供电。

此致、

尼克

嗨、Nick、非常感谢您的帮助! 我将尝试进行最后一个测试、我认为分析 LDO 输出端电流的方向会有所帮助

如果电流流出、则可以实现您的解决方案、我认为设计没问题。

如果电流流入、则有功功率限制处于活动状态、我们必须考虑该设计。

通过分析二极管耦合的引脚1和2上的电压、我得到了输出可视值:

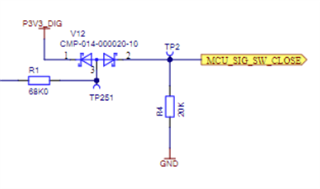

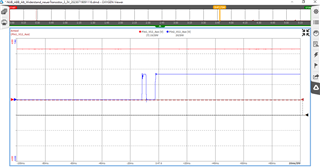

如下图所示:

可以看出、LDO 输出确实没有影响、如红线所示。 蓝色线是到 MCU 的输出、运行良好。 S、我认为、 即使我直到现在才真正了解该机制、对输出没有影响、整体设计也是可以的。 再次感谢您的帮助、

此致