迪亚尔斯、

如果 DSG 引脚锁存为低电平、是否会导致 BQ76952复位?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Andrew:

DSG 引脚被锁存至多高的电压电平? 通常、当不驱动栅极时、DSG 引脚将被拉至负载(PACK+)电压。 但是、如果未完全使用该引脚、建议将该引脚保持悬空、而不是将其连接到 GND。 始终有一种情况、即如果您尝试将其锁存到一些小电压(接近 GND)、然后尝试导通引脚、大电压差可能会导致问题、但这似乎不太可能。 您目前在电路板上看到的这种现象是否存在?

此致!

A·内德尔费尔德

尊敬的 Asher:

客户发现 有时发生短路时无法观察到 SCD 位、 在这种情况下、DSG 会在短时间内下拉至负电压、同时、 我们可能会看到放电 MOS 的 VGS 急剧下降、REG1缓慢下降。

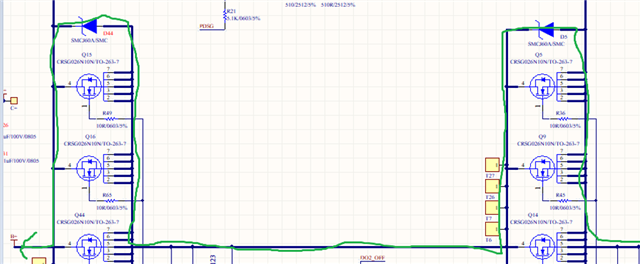

我对随附的原理图和波形的问题进行了总结,您能否帮助进行审查并提供如何解决此问题的建议?

非常感谢!

尊敬的 Andrew:

看看您发送给我的那部分原理图、我有几个问题:

1. DSG 和 CHG 的闸门是由什么驱动的? 看起来它们由同一个源驱动、而不是由另一个

2.您的客户使用多大的电阻作为电流检测电阻?

3.存储在以下寄存器中的三个值是什么:Protections:SCD:(Threshold、Delay、Recovery)

4. D44和 D5的要点是什么? 这两者的结合使我认为您永远无法禁用充电、因为电流始终会流过它们。

有没有其他方法可以看到 BQ76952的完整原理图? 了解 FET 的驱动机制和 SRP/SRN 引脚配置会有所帮助吗?

此致!

A·内德尔费尔德

尊敬的 Asher:

CHG 和 DSG 由 BQ76952驱动、充电和放电端口是分开的、因为客户添加了 MOS (放电操作由 MCU 控制、符合 ISO13849安全要求)与放电 MOS 串联、因此可能会给原理图的一部分带来困惑。

电流传感器为1m Ω、SCD 设置为:SCD 阈值、300mV;SCD 延迟、200us;恢复时间、 60秒。

根据 与客户的讨论、我们发现2点可能很重要:

1.虽然未触发 SCD 位、但在发生短路时正确触发了 DSG_TEST 位。 这意味着 bq76952确实关闭了放电 MOS、因此问题在于 SCD ALERT 位未正确设置的原因

2. VDSG 可以被拉至约0V,正确吗? 当发生短路而 SCD ALERT 位未正确触发时、关断放电 MOS 时、VGS 最终会急剧下降、从而导致 VDSG 处出现负脉冲(如我的总结所示)、该负脉冲是否会导致 BQ76952关断 (如果器件未关断、那么一旦波形显示是否设置了 SCD ALERT 位、DSG/LD/P+可能会被负载检测电路拉高)?

由于原理图是机密信息、我无法将其放在这里、因此我会 通过电子邮件发送给您。

非常感谢!

尊敬的 Andrew:

为了说明这一点、您是说0x0057 Manufacturing Status ()寄存器中的 DSG_TEST 位设置为高电平还是 DSG_FET 位设置为高电平? DSG_TEST 位用于禁用保护的测试模式。 Settings:Manufacturing:Mfg Status Init[FET_EN]位的值是多少? 如果该位设置为0、则将其置于测试模式。

如果器件短接足够长、VDSG 将被拉至0V、因为器件会失去正常情况下从非短接电池汲取的电量。 足够长的短路就足以拒绝 BAT 引脚提供足够高的电压、从而使器件正常运行并使其进入 SHUTDOWN 模式。

此致!

A·内德尔费尔德

尊敬的 Asher:

您是正确的、我与客户进行了仔细检查、 他们可能发现在执行短路时、0x7f (FET 状态)寄存器的 DSG_FET 位没有响应。

客户尝试添加肖特基二极管来限制 DSG 上的负脉冲、但没有改善。

客户移除了 D12、可能会触发 SCD ALERT 位、但在3次短路测试后 DSG MOS 烧坏。

"足够长的短路就足以拒绝 BAT 引脚具有足够高的电压、从而使器件正常运行、并导致其进入 SHUTDOWN 模式。"、但 当 无法设置 SCD ALERT 位时、短路时间与正常情况类似。

因此、问题可能会转向为什么 Vgs 有时急剧下降(测试条件完全保持不变)? 负脉冲会导致器件关断吗? 如果不关断、为什么无法观察到 SCD 警报?

非常感谢!

尊敬的 Andrew:

几个简短的问题:

是否设置 FET_EN 位?

2.能否在 SCD 测试期间发送 SRP 和 SRN 的示波器捕获。 查看引脚上的差分电压以及 SRP 相对于 VSS 和 SRN 相对于 VSS 的电压都会有所帮助。

您提到您使用的是 MCU。 器件通电后是否立即尝试写入器件? 如果不是、您可以尝试读取0x12 Battery Status ()寄存器中的 POR 位、以查看自上次退出 CONFIG_UPDATE 模式后是否发生了完全复位。 我已从数据表中简要说明了 POR 的作用。

4. Vgs (和 DSG 引脚)的负值有多大? 该引脚的额定值比 VSS 低-0.3V、因此可能会引起一些问题。

我注意到 SRP 和 SRN 上没有 VSS 滤波电容器。 通常建议在每个引脚和 VSS 之间连接一个电容器(~ 0.1uF)。 我建议添加这些函数、看看这对性能是否有帮助。 我在下面附上了一个示例:

此致!

A·内德尔费尔德

尊敬的 Asher:

我将您的问题的答案和波形附在后供参考:

e2e.ti.com/.../BQ76952--SCD-bit-issue_2D00_20230713.docx

在 SRN/SRP 中添加0.1uF 电容器后、SRN/SRP 上的电压脉冲可能会被消除、并且可能会在不燃烧 MOS 的情况下正确触发 SCD ALERT 位。 似乎这个解决方案是正确的。 但是、客户希望在解决问题之前确认问题的根本原因。

非常感谢!

尊敬的 Andrew:

这与 SRP/SRN 引脚的设计方式有关。 当两个引脚都达到相对于 VSS 过高的电压(因为它们旨在连接或靠近 VSS)时、器件将进行硬件复位、而不会清除数据或 RAM 存储器。 当发生短路并且相对于 VSS 的电容器不存在时、形成的电压尖峰足以触发此复位。 然而、在添加电容器时、电容器会在尖峰出现时对 VSS 短路、因此两个引脚上的电压绝不会相对于 VSS 上升太大、并且器件会看到更高的电流并触发 SCD、而不是硬件复位。

此致!

A·内德尔费尔德