您好、TI 团队、

我有一个用于开关转换器的典型 H 桥、其中两个 UCC27211A (一个用于超前/滞后桥臂)共享相同的 Vdd。 我们有意使用 UVLO 功能、通过在 PCBA 处于复位状态时将 Vdd 从12V 降低到6V 来防止开关。 我预计当 Vdd 是6V 时、栅极驱动器不应有输出 PWM、因为输出将变为 Hi-Z。

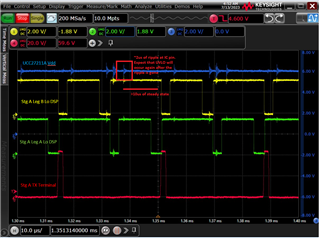

但在我的测试过程中、当 Vdd 为6V 并且我的 DSP 正在驱动输入 PWM 时、我看到栅极驱动器输出偶尔开启。 请查看所附的示波器截图:

放大:

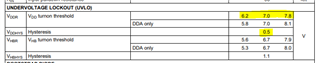

我知道、根据此处的数据表、存在一些迟滞+元件变化:

我有3个问题:

1.栅极驱动器芯片导通后的 UVLO 关断阈值是否等于 Vdr - Vddhys = 6.5 (典型值)?

2.在这些示波器镜头中看到的噪声是否足以在短时间内开启栅极驱动器?

3.我们现有的 PCBA 只能将 Vdd 降至最低6V、因此我们将无法覆盖基于 Vdr 锁定阈值的整个元件变化范围。 您能否提供此参数的最小/典型/最大展频的分布曲线?

谢谢。

瑞克