主题中讨论的其他器件: UCC21750、UCC12050、 UCC21551

大家好!

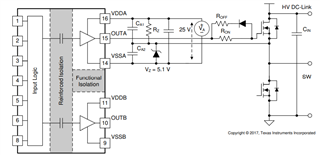

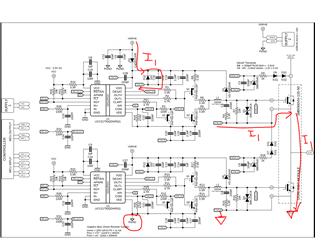

我正在使用 UCC21755-Q1构建一个带有升压器的半桥电路。 但是、我在使用 VEE (负电源轨)和 DESAT 时遇到了问题。 为了避免产生混淆、我将尝试用单独的章节来解释我面临的设计问题。

DESAT 问题

考虑到我们将使用2MBI300VH-120-50 IGBT 模块和+15V 高驱动电压、根据 IGBT 的技术文档、我们需要7~8 μ V 的 DESAT 阈值。 但是、UCC21755-Q1具有5V 的 DESAT 阈值电压。 减去电阻器和二极管两端的压降、可以得出3.4V 的近似阈值电平。 这是不够的。

问题1:您是否可以建议一种提高 DESAT 阈值水平的方法? (可能需要不同的器件)

问题2:您能提供任何设计建议或提示吗?

VEE 问题

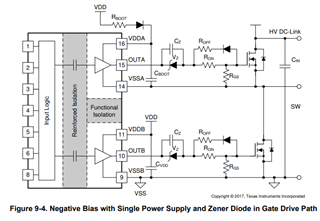

为低侧驱动器获取负栅极电压相对容易、但我正在为高侧应用类似的方法。

Q3:您能否建议一种向高侧驱动器施加负栅极电压的方法?

Q4:对于图中所示的驱动器部分的设计、您有什么建议或警告吗?

此致、