主题中讨论的其他器件: TPS40304

TPS40304A 器件有两个问题。

1.输出电压与配置值不同。

预期电压为3.3V、但有效电压为2.4V。

尽管它是不校正电压、但在斜升后、Iout 可以超过15A 的电流。

2.如果我在斜升前将 ILOAD 设置为任何电流,设备将无法正常启动。 (无输出电压)

这是我的 配置。

输入电压:+12V 直流

器件:TPS40304A (非 TPS40304)

我应该如何检查 这些问题?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TPS40304A 器件有两个问题。

1.输出电压与配置值不同。

预期电压为3.3V、但有效电压为2.4V。

尽管它是不校正电压、但在斜升后、Iout 可以超过15A 的电流。

2.如果我在斜升前将 ILOAD 设置为任何电流,设备将无法正常启动。 (无输出电压)

这是我的 配置。

输入电压:+12V 直流

器件:TPS40304A (非 TPS40304)

我应该如何检查 这些问题?

Unknown 说:2. 如果我在斜升之前将 ILOAD 设置为任何电流、则器件不会正确启动。 (无输出电压)

从 SS 到 GND 的1nF 电容器正在对60μs 软启动时间进行编程、此时电容680μF 为3.3V、为输出电容器充电所需的电流几乎为38A、在输出端存在任何负载的情况下、您很可能会触发 OCP 并强制关断。

我建议将 CSS 电容器的值增加到10到47nF 之间、以实现更可控的软启动。

预计电压为3.3V,但有效电压为2.4V。

电阻分压器似乎是针对输出电压= 3.24V (Vref / Rbias) x (Rfb + Rbias)设置的

电压较低可能是稳定性问题导致的。 虽然在使用列出的2个具有200mΩ ESR 的330μF 电容器时输出显示为稳定、但如果使用具有较低 ESR 的电容器、则环路不稳定。 仔细检查输出电容器 ESR 电平。

这是我自己的硬件和布局。

我懂了。 请告诉我您使用较低 ESR 电容器的实验结果是什么。

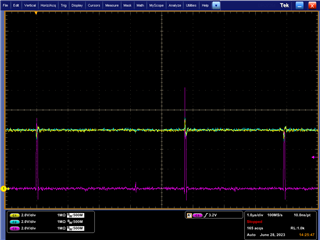

如果问题仍然存在、请使用示波器来测量每分段2或5μs 的开关波形。

1.应用+12V 拉电流电源。

2.捕获的开关 节点

3.EN/SS 线路上的电容器:一个100nF 陶瓷电容器

VOUT 上的电容器:一个330uF (ESR 16m Ω)、两个10uF 陶瓷电容器。

5. III 类补偿计算工具的配置文件(修订版 E)

e2e.ti.com/.../TPS40304A_5F00_3.3V.xlsm

我认为 Vout 问题是由占空比引起的。

此配置也不起作用。

您的波形都显示 Vout = 0V、我相信我们会看到初始启动、或者可能出现故障重新启动。 我们能以10ms/div 的间隔查看 VOUT 和 SS 吗?

您是否还可以对 TPS40304A IC 引脚处的 VIN 和在 100ns/div 高侧 FET 上升沿触发的高侧 FET 漏极处的 VIN 进行振荡测量?

TPS40304A 具有高侧电流限制检测功能、在高侧 MOSFET 开关期间、如果高侧 FET 的漏极电压降至 VIN 引脚电压以下、则会触发高侧电流限制检测功能。 当进行检测时、高侧 FET 导通时间将终止、以保护 MOSFET 免受损坏。

高侧 FET 的 VIN 和漏极连接到同一源极、无需任何串行元件(例如磁珠)。

因此、 VIN 不应降至漏极电平以下。

[/报价]我知道没有串行元件、但即使没有串行元件、PCB 布线的寄生电感也会在高侧 FET 开关期间导致 VIN 布线上出现显著的压降。 这可能会导致 MOSFET 漏极处的 VIN 显著低于 TPS40304A 的 VIN、从而可以触发高侧电流检测和终止导通时间脉冲。 如果您可以提供、可以提供在 TPS40304A 引脚上测量的 VIN 振荡示波器图像、该图像以100ns /分段的速率测量高侧 FET 的漏极或高侧 FET 的开关节点(如果您有3个可用通道、则可以提供两者)、 它将帮助确定这是否是问题所在。

为了提高测量的分辨率、请对通道和直流失调电压使用相同的0V 参考点、以便以尽可能高的分辨率显示 VIN 和正 SW/漏极值。 请勿使用交流耦合。

您还可以测量 TPS40304A 的 COMP 和 FB 引脚的电压吗? (请勿在 COMP 引脚上放置示波器探头、因为这样会对误差放大器补偿和性能产生负面影响。

这些栅极驱动波形看起来极慢、高侧 FET 栅极在300ns 时从1.5V 充电至略低于5V。 TPS40304A Ω 6.5V 稳压器和1.5k Ω 上拉驱动器。 为栅极电压充电所需的时间不应超过300ns。 输出电压受到限制的原因是、高侧短路保护将导通时间限制为300ns、因为 MOSFET 未完全导通。

您是否有与自举电容器或高侧 FET 栅极串联的电阻器?

您所使用的 MOSFET 的实际器件型号是多少?

1. BOOT 电阻在高侧 FET 栅极上经过了2.2欧姆至68欧姆但0欧姆的测试。

FDMS3600S 用于 MOSFET。

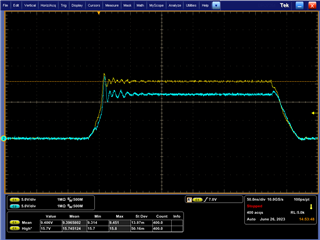

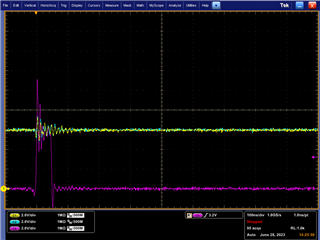

2.高侧 FET 栅极(黄色)和 SW 节点(青色)。

VDD = 5V、VIN=12V、HGATE = 1欧姆、BOOT 上的电阻= 1欧姆

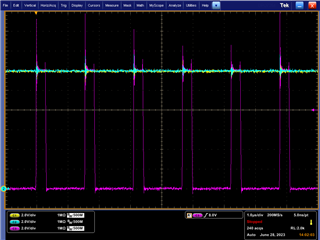

3.低侧 FET 栅极(青色)和 SW 节点(黄色)。

VDD = 5V、VIN=12V、 LGATE = 0 Ω、BOOT 上的电阻= 1 Ω

1) 1)请提供您当前使用的实际原理图、包括所有组件。

2) 2)请提供以下波形:

波形1:

TPS40304A 引脚上的 SW (直流耦合、2V/div、从屏幕底部向上+1间隔的接地)

TPS40304A 引脚 上的 VDD (直流耦合、2V/div、从屏幕底部向上+1间隔的接地)

高侧 FET 的漏极 (直流耦合、2V/div、从屏幕底部+1间隔的接地)

如果示波器允许在1V/div 条件下存在-6V 的偏移、请将所有波形更新为-6V 偏移和1V/分频)

波形2:

重复波形1、将电源电压从12V 降低到较低的电压(介于5V 和8V 之间)

占空比/SW 高电平时间是随 Vin 降低而增加还是保持不变?

输出电压是变化还是保持不变?

波形3

在向 VOUT 施加10A 负载电流时重复波形1

3) 3)请使用电压表提供相对于 PCB 上同一接地点的以下测量值

VDD、SW、BP、FB、COMP、 接地时应尽可能靠近 IC。

3) 3)您组装了多少块电路板? 是否所有电路板都显示相同的行为?

4) 4)此 TPS40304A 从何处购买? 您能否提供器件顶部图片以及卷带或运输包装中的标签?

1.实际原理图

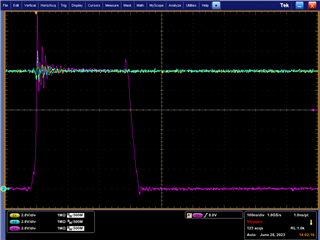

2.波形1

3.波形2 (6.1V VDD)

4.电压电平

(1) VDD:11.97V

(2) SW:2.41V ~ 2.48V

(3) 6.492V

(4) FB:0.425V

(5) COMP:1.008V

(6) GND:0.0000V ~ 0.0001V

5. 两块板已组装且具有相同的行为。

6. 从 mouser.com 购买,芯片组的标记是,

304A

25J

P7FJ

此致、

VDD = 6.1V 时的开关节点波形看起来像是在150-300kHz 下的50ns 脉冲(脉冲跳跃)

这些是否在启动期间进行、或者当 VIN = 6.1V 时、转换器是否产生非常小的电压?

FB 显然不应调节至0.425V、我也看不到您的电路中会阻止它调节至预期的0.591V、也看不到会导致它在 VDD = 6.1V 时跳过50ns 脉冲的任何内容

我将检查该器件代码、但根据 TI 客户退货政策、对于从经销商处购买的器件、您需要联系经销商。 https://www.ti.com/support-quality/additional-information/customer-returns.html

我昨天没有看到这件事,很抱歉,但我相信我发现了问题。 使用来自 VIN 的电阻分压器驱动 EN/SS 引脚、 即在 VIN = 12V (以及 VIN = 6.1V 时为0.6V)时将 EN/SS 电 压限制为1.2V (而在 VIN = 6.1V 时为0.6V)。该分压器防止软启动电压充分上升、以允许内部基准控制从软启动输入到误差信号放大器的 FB 稳压。

TPS4030xy 系列器件用于通过开漏源驱动 EN/SS 引脚、使用内部 EN/SS 电流源对外部 SS/EN 电容器进行充电和放电。 EN/SS 需要至少上升至1.4V (带余量的1.8V)、以确保0.591V 基准控制误差放大器和调节。 EN/SS 引脚可能需要高达2.0V 的电压以确保启用欠压保护(UPV)。

要确认这是问题的根源:

1) 1)将 R15从10k 增大到20k

或

2) 2)将 R14从100k 减小到51k