TI 员工、您好!

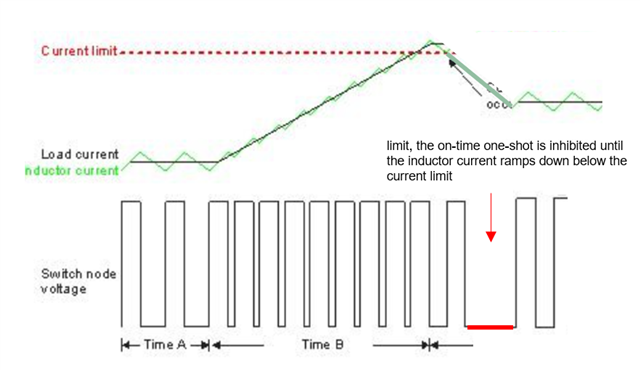

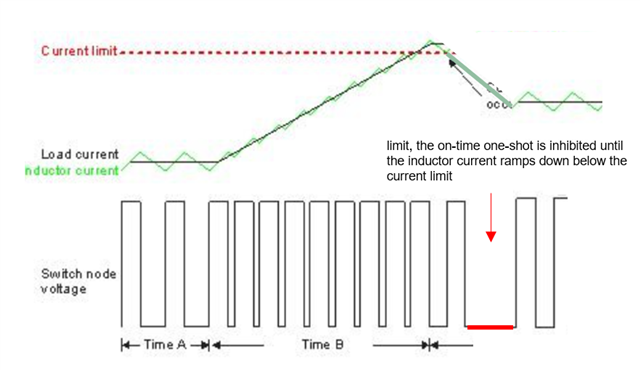

我对 TPS56C215中的谷值电流限制有疑问。 恐怕会产生误解、因此我编辑了 E2E 帖子中的一个图供您参考。 您能否告诉我下面的波形是否解释了过流期间的谷值电流限制?了解谷值电流限制-电源管理-技术文章- TI E2E 支持论坛

另外、您能否告诉我电流限制是多少(低侧负电流)? 电流是否定义为从低侧整流器 FET 的源极到漏极的方向?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TI 员工、您好!

我对 TPS56C215中的谷值电流限制有疑问。 恐怕会产生误解、因此我编辑了 E2E 帖子中的一个图供您参考。 您能否告诉我下面的波形是否解释了过流期间的谷值电流限制?了解谷值电流限制-电源管理-技术文章- TI E2E 支持论坛

另外、您能否告诉我电流限制是多少(低侧负电流)? 电流是否定义为从低侧整流器 FET 的源极到漏极的方向?

您好!

底部的图是正确的。 根据数据表、负电流限制设置为4A 典型值。 仅当您使用 MODE 电阻器组合将器件设置为在 FCCM 下运行时、才会发生这种情况。 如果设置为 Eco-mode、则电流不会低于零。 如果您已将器件设置为在 FCCM 模式下运行、则在导通时间内、电流将流经 HSFET、从 Vout 到 VIN。 在关断期间、针对4A 谷值限制监测的 LSFET 电流将通过电感器从 Vout 流向 LSFET 的漏极和源极、然后再返回。 在死区时间期间、HSFET 体二极管将允许电感器电流通过输入电源和电容器。 希望这对您有所帮助。

谢谢。

阿莫德