主题中讨论的其他器件:TPS23523、、 CSD19535KTT

尊敬的团队:

在设计 TPS23523时、我有几个疑问。

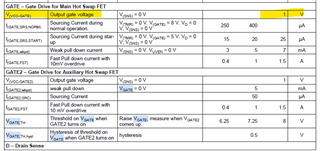

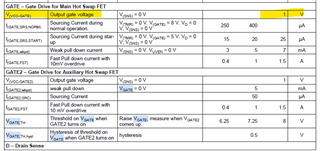

#1. 从 TPS23523的数据表中、我们可以看到、 如下表所述、栅极输出驱动电压最大为1V。 因此、我在这里的理解是、此引脚上的最大栅极驱动电压将仅为最大1V。 是不是啊?

从建议的运行条件中也可以看到、栅极引脚输出电压介于0到 VCC 之间、如下所示。 在本例中、我使用18k 电阻器将 VCC 引脚连接到接地端子。 那么、请告诉我实际的 VCC 和栅极引脚电压将是多少。?

在 TPS23523EVM-863评估板上、您使用的 Q3- MOSFET 是 CSD19535KTT、它的最低要求是 VGS (th) 2.2V。 由于 TPS23523器件的栅极引脚仅提供1V 输出、因此该 MOSFET 永远不会导通。 请帮助我理解。

#2. 此外、栅极 电压在下表中称为 V (VCC GATE)。 它的意义是什么。 请解释一下。

#3. 在我的 设计中、我们 使用-48V 电源。 我们使用100E 电阻将-48V 线路连接至 TPS23523的 NEG48引脚。 并将 VEE 引脚接地。 栅极引脚连接到热插拔 MOSFET 的栅极(NTB004N10G),其 Vgs 最大值为+/-20V,但由于 MOSFET 的源极连接到-48V,而且如上所述,TPS23523的栅极输出电压为1V,因此得到的 VGS 将接近-48V。 这违反了 MOSFET 规格。 您的评估板也是如此... 但此设计正在正常运行... 我很困惑... 我想我缺少理解的东西。 请提供您的澄清。

谢谢

Pradeep。 S