您好!

对于使用 UCC28070的半桥 PFC、您能帮助回答这个问题吗:

控制器如何识别 PFC 配置是交错还是半桥配置。 我们的理解是、控制器在2个 FET 之间生成180度相位差输出、这是交错 PFC 所需的、但半无桥不需要。

我们在 参阅以下文档、但找不到控制器运行的两种拓扑之间的区别因素。

UCC28070实现无桥功率因数校正(PFC)前置稳压器设计 https://www.ti.com/lit/an/slua517/slua517.pdf

谢谢、Keith

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

对于使用 UCC28070的半桥 PFC、您能帮助回答这个问题吗:

控制器如何识别 PFC 配置是交错还是半桥配置。 我们的理解是、控制器在2个 FET 之间生成180度相位差输出、这是交错 PFC 所需的、但半无桥不需要。

我们在 参阅以下文档、但找不到控制器运行的两种拓扑之间的区别因素。

UCC28070实现无桥功率因数校正(PFC)前置稳压器设计 https://www.ti.com/lit/an/slua517/slua517.pdf

谢谢、Keith

Keith、您好、

UCC28070控制器不区分两种 PFC 拓扑(或任何其他拓扑)。 它仅根据所有输入(基本所有其他引脚)上的信号驱动其输出(基本上是 GDA 和 GDB 引脚)。

UCC28070控制器设计用作两相交错 PFC、它"认为"即使重新配置为不同的拓扑、仍在这样做。

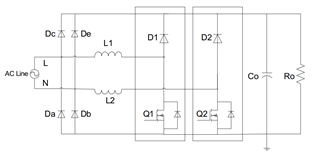

事实证明、半桥无 PFC 配置与 UCC28070的工作信号兼容、并且该拓扑利用单独的交错输出来驱动其中一个 MOSFET (例如参考应用手册图4的 Q1) 在输入正弦波的正半周期内驱动另一个 MOSFET (Q2)、在正弦波的负半周期内驱动另一个 MOSFET (Q2)。

实际上、两个 MOSFET 是同时驱动的(同时在相同的开关频率下、但有180度异相)、但电桥的一半在电感器上不会产生电压、因此在该半个线路周期中不会有电流流动、而所有电流在另一半周期中流动、 反之亦然。 UCC28070的两个相位在很大程度上相互独立、尽管它们都接收相同的 IMO 基准和相同的 VAO 误差信号。 在半线周期中、一个相位没有电流、因此该相位的电流放大器输出 CAOx 处于最大水平(和最大 PWM 占空比)、但 无法产生电流、而另一个相位通常作为单相升压 PFC 运行。 这种情况在接下来的半线周期中逆转到另一个阶段。 每个半个周期有一个 MOSFET 在无电流的情况下开关、这一事实不会产生明显的后果(尽管会产生栅极驱动损耗)。

一般情况下、除非另外特别设计、否则这个控制器和大多数其它控制器并不"知道"它们所使用的拓扑或配置、而只是根据出现在它们输入上的信号按照设计运行。 不同的拓扑 可以 利用这些行为实现不同的设计目标、这通常 具有某种优势(例如消除桥式二极管损耗)、但会以某些其他方面为代价(例如两个相位中没有交错电流)。

此致、

乌尔里希

您好!

需要确认一点。 假设在正半个周期内、器件 Q1、D1 (1-D 周期期间)、Q2的体二极管和慢速二极管 dB 将导通。

因为我们说 Q2的 PWM 将处于最大值。 占空比下、Q2在该期间保持完全导通。 因此、Q2实际上将在该期间内看到导通损耗。 是这样吗? 我知道它会变小、因为这将取决于 Q2和 dB 之间的电流共享。 只是为了确保分别考虑每个半个周期内 Q2和 Q1上发生的损耗。

谢谢、Keith

Keith、您好、

是的、回答正确。 在实际情况下(非理想)、L2确实会在 Q1的1-D 间隔期间累积一些电流(在负方向)、而 Q2开启。

由于在这种情况下 Q2充当同步整流器,因此与 dB 相比,它将具有非常低的压降,因此在 L2上应用 VDB,持续时间为(1-D)*TSW,因为 D 在线路周期内变化。

实际上,每个开关周期,Q2仅在 DMA*TSW 下打开,但 DMAX 通常设置在95%左右,因此可以将其简化为100%,并应用校正因子来计算1-DMAX 间隔期间的体二极管损耗。 只有当 Q2关断时 L2通过体二极管拉取电流时、体二极管才会导通。

同时、L2电流 在 Q1的1-D 间隔内由 VDB/L2建立、在 Q2的1-DMAX 间隔内由-VQ2/L2衰减。

也许可以计算 Q1的平均1-D 间隔、但我没有现成的数学方法。

在升压转换器中、1-D = Vin/Vout、因此1-D (t)= Vin (t)/Vout。

在 Vin_pk 接近 Vout 的最高直线下、我们可以大约1-D 接近0%、当 Vin = 0V 时、1-D = 100%、因此(1-D) avg 为~50%。

在 Vin_pk 远离 Vout 的最低线路上、我们可以大约1-D 为>50%、当 Vin = 0V 时、1-D = 100%、因此(1-D) avg 可以为 75~80%(例如)。

因此、在概念上、L2电流可以累积到 I_L2_pk =(VDB/L2)* 10mS*80%(例如在50Hz 线路上)。

由于半个线路周期(在本例中为10ms)是一段很长的时间、L2电流似乎会超过 L1电流。 如果是、则二极管 DE 将起作用、因为交流源电流不应超过 L1电流。 我不认为会发生这种情况、但我不确定、因此我不知道可以累积多高的 L2电流。

此致、

乌尔里希