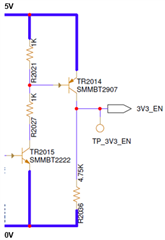

您能否提供 TPS82130 EN 输入电路原理图? 我正在查看一个 TPS82130电路、该电路会生成3.3V 电压、其中 VIN = 3.6V、EN 输入由以下电路提供。 我需要弄清楚为什么它的 EN 信号3V3_EN 保持在大约2.3V、以及 TPS82130器件是否由于 EN 输入电压可能超过其 VIN + 0.3V 的绝对最大额定值而被损坏、然后被拉低至2.3V。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您能否提供 TPS82130 EN 输入电路原理图? 我正在查看一个 TPS82130电路、该电路会生成3.3V 电压、其中 VIN = 3.6V、EN 输入由以下电路提供。 我需要弄清楚为什么它的 EN 信号3V3_EN 保持在大约2.3V、以及 TPS82130器件是否由于 EN 输入电压可能超过其 VIN + 0.3V 的绝对最大额定值而被损坏、然后被拉低至2.3V。

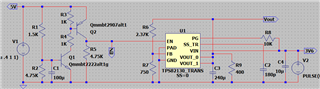

我根据您的建议使用 TPS82130_TRANS.LIB 运行了 LTSPICE 仿真。

仿真显示、当 PNP 晶体管导通时使能 EN 输入被上拉至5V、并且根据实际电路没有保持大约2.3V 的电压。 因此、TPS82130模型不能反映现实、并且仿真不准确、或者这是电路应该执行的操作、并且我们没有问题、因为2.3V 的 EN 输入处于其工作限制范围内。 或者、我们给了损坏的 TPS82130转换器。 你能说这是什么情况吗?

尊敬的 Kevin:

您在 EN 引脚之外设计电路的目的是什么? 是否要通过5V 信号控制 EN? 如果需要、您可以只使用两个电阻器来进行5V 电压分压。

在您的电路中、当 Q2打开时、5V 电压将直接进入 EN 引脚。 由于 VIN 仅为3.6V、VIN 和 EN 之间的内部 ESD 二极管将导通、然后5V 和3.6V 电源轨短路。 因此可能会损坏器件。

我认为您应该添加一个高于 Q2的电阻器来限制直接向 EN 引脚提供5V 的电压。

希望这可以帮助您。

此致、

石屏市

感谢您的答复。

我没有设计电路、因此无法解释为什么以这种方式进行设计、可能是出于疏忽。 这些转换器中有许多可为 FPGA 提供0V95、1V0、1V2、1V8和3V3。 Q2左侧的电路是一个序列发生器电路、其他转换器使用类似的电路以正确顺序为 FPGA 电源上电。 出于某种原因、3V3转换器由3.6V 电源供电 、而0V95、1V0、1V2和1V8转换器由5V 电源供电、因此我们不存在这些问题、但出于某种原因、3V3转换器由3.6V 电源供电。

如果通过将 EN 拉至5V、我们要在 VIN 和 EN 之间打开 ESD 保护二极管、为什么 EN 保持在大约2.3V、即低于 VIN = 3.6V、而不是介于 VIN = 3.6V 和5V 之间?

很遗憾、根据您3月19日的电子邮件、问题仍未解决。 使用我们的现有 EN 驱动电路、我们会看到 EN 输入约为2.3V 的一些单元、而 EN 输入约为4.5V 的一些单元、这意味着 EN 输入 ESD 二极管已导通但未发生故障。 我们有一个器件的电压为4.49V、用于我们的多次通电/断电加速寿命测试活动。 裸片是否发生了变化或您是否使用不同的制造工厂来解释为什么某些 TPS82130转换器比其他转换器更强大? 同样、我们对 EN 输入电路原理图很满意、这样我们就可以确定对当前设计的可靠性影响。