尊敬的支持部门:

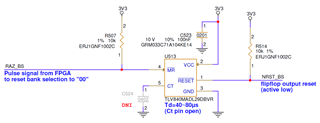

我在设计中使用 TLV840MADL29DBV 为 FPGA 生成的复位信号添加延迟。

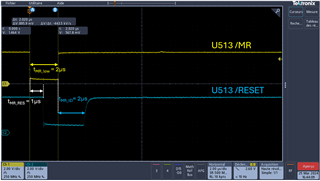

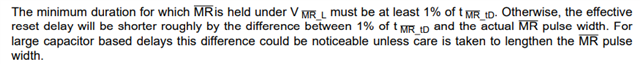

FPGA 使用2us 低电平脉冲驱动/MR 输入、以开始将/RESET 置为低电平(因此2us > TMR_pw)。

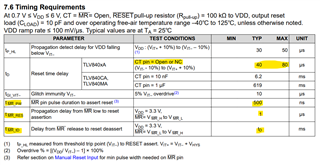

我将 CT 引脚保持断开、因此延迟应该为数据表 p7中所述的典型值/80us 最大值。

~我的理解、在/MR 再次为逻辑高电平后、延迟电路应在40 μ s 80us 内保持/RESET 低电平。

我测试了函数、但/RESET 输出仅在2us 内驱动为低电平、释放为高电平...

请查看随附的原理图和示波器捕获。

我漏掉了什么东西吗? 您能否澄清这一点?

非常感谢您的帮助。

此致。