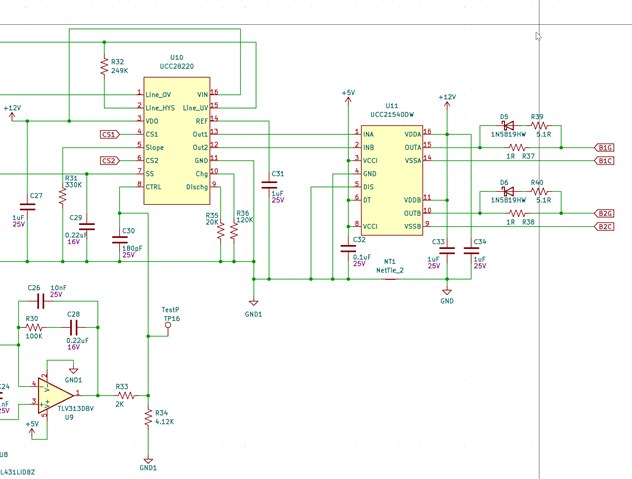

主题中讨论的其他器件: UCC28220

您好!

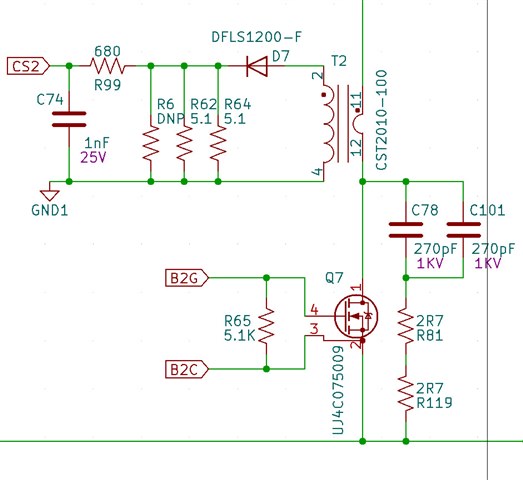

在交错升压电路上、UCC21540A 似乎存在布局问题。

我们确信此电路运行良好、因为我们的版本不存在此问题。

逻辑侧由5V 电源供电、每个输出使用12V 电源时处于相同电势。

我们正在以100KHz 的开尔文连接驱动4引脚 MOSFET、并且死区时间已禁用。

在最新版本中、我们使驱动器更靠近 MOSFET、并且随着我们启动功率、21540A 过热。 (如100摄氏度+++)

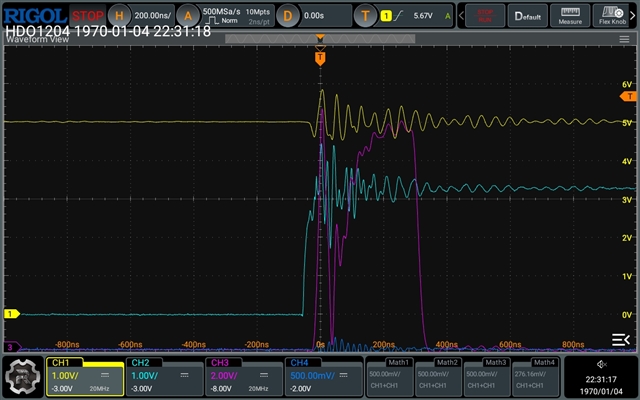

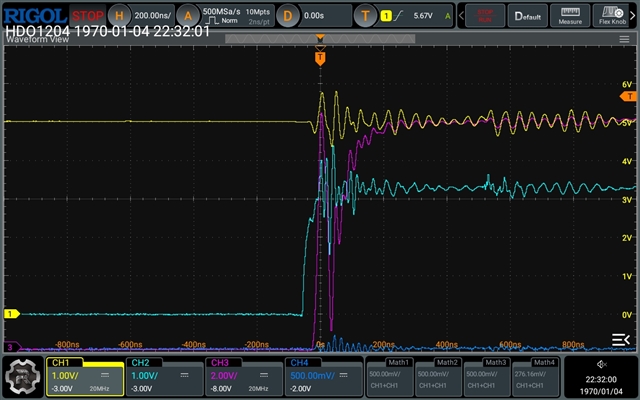

乍一看、电源似乎有更多的噪声。 我们试图增加去耦、但变化很小。

我的问题是这个。

初级侧或驾驶员侧的电源噪声(毛刺脉冲<100ns)是否会与 UVLO 电路接合?

如果 UVLO 偶尔接合、这是否会使器件的温度升高那么多?

还有哪些其他因素可能导致器件温度升高?

谢谢!

米歇尔