Other Parts Discussed in Thread: LM5122

我正在尝试验证一个八相升压转换器设计、但在我们从 DCM 转换到 CCM 之后、输出电压会立即发生折返/衰减。

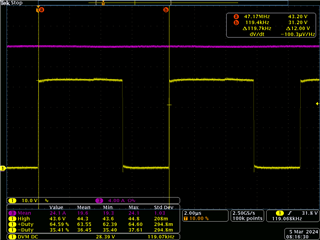

下面是我看到的一个示例:

上图是 VOUT。 在图的开头、转换器是稳定的、负载为20A -正好是转换器不连续时的边缘。 然后我将负载增加到25A、电压立即从43.7V 下降到43.5V。 电压立即开始稳定衰减、直到达到42.9V、在降至42.5V 之前先稳定了一段时间、此时电压立即再次开始衰减。

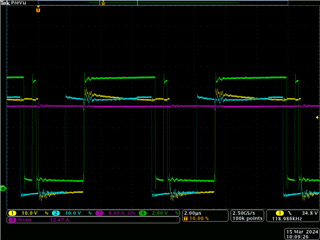

我的测试设置如下所示:

- V_IN=28.16V

- 输出电压= 43.8V

- I_LOAD = 20A 至25A 至20A

我注意到的一点是、如果我直接在控制器芯片上使用一罐冷冻喷雾、电压会立即恢复一秒钟、然后再下降-这让我觉得我看到的问题与温度有关; 不过、在使用温度传感器探测各种元件时、似乎没有什么物体会变得过热。

我还注意到的另一点是、反馈电压随着输出电压而下降。 它的起始电压为1.2V、但衰减速度也与输出电压看起来相同。

以下是展示主转换器以及从转换器的原理图- 6个其他从转换器的配置与此处的配置几乎相同-(如果需要、我可以提供更详细的原理图):

对于我正在使用的组件、我应该考虑哪些因素、这些因素可能会为我提供所获得的结果?

感谢您的帮助!