Other Parts Discussed in Thread: LM5122

报告中已经出现了标题相同的类似问题。 我们面临 SW 节点对 AGND 短路。 这可能是什么原因造成的? 下面是一些设计信息:

我们将使用 LM5122Z 作为升压转换器、以在最高 0.8A (大约50W 输出功率)、对应于18-33V (典型值)之间的输入电压范围12 - 40V (紧急状态持续数十秒)。 开关频率约为210kHz。

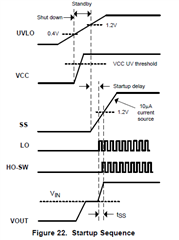

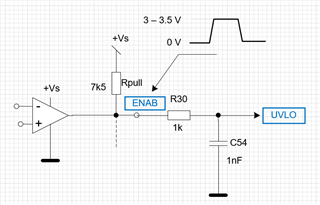

在以下条件下发生故障:输入电压升高到51V、这会触发我们自己的电压监控器并通过 UVLO 引脚(连接到低电平)禁用 LM5122。 在我的观察中,如果我们将电压降低到大约49V,则 SW 节点会发生故障,从而再次启用 LM5122。 我听到了来自电源组件转换器的奇怪的噪音。 输入电源开关关闭后、我们注意到 SW 节点对 AGND 短路。

我们有一个输入电压瞬变限制器、它可以在任何情况下将输入电压限制到53 - 54V、与输入瞬变无关。 因此、输入电压远低于任何最大额定值(例如、VIN 或 CSP SCN 引脚等)。

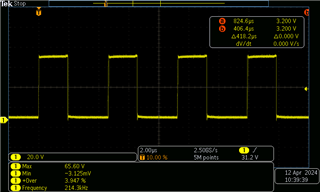

在采用类似设计的另一个电路板上、到目前为止、我们没有遇到任何问题。 在此情况下、我还通过示波器测量了 SW 节点-因此在 LM5122重新启用(低于我们自己的 OVLO 释放阈值大约49V)后、捕获了 SW 节点处的第一次开关脉冲。 是否在某些情况下输入电压被添加到输出电压上。 根据我的理解、升压转换器不会出现此行为、因为转换器开关处于低侧。

我可以再次使用另一个电路板进行检查、但希望通过此类测试避免杀死太多的 LM5122。 因此、我想知道理论上器件发生故障的可能原因。 我的专用问题。

Q1:SW 节点对瞬变的敏感度

Q2:在不影响效率的情况下减少 SW 节点瞬态过冲的正确方法是什么。

->我想-5V 额定值不会有任何问题、因为低侧 MOSFET 的体二极管钳位到大约-1V。

Q3:SW 节点上的损坏仅是副作用吗、并且是由另一个引脚过压引起的

安德烈亚斯