您好!

当负载器件为使能时、VREG 下降并且 VOUT (1.2V)停止。 在大约6uS 之后、VOUT 上升并再次停止。

由于 VREG 引脚低于3.95V 的阈值、这似乎为 VOUT (1.2V)停止。 然而、VDD 引脚(4.5V 至25V)和 EN 引脚(0.6V)在一段时间内不会低于阈值。

你知道这是什么原因吗?

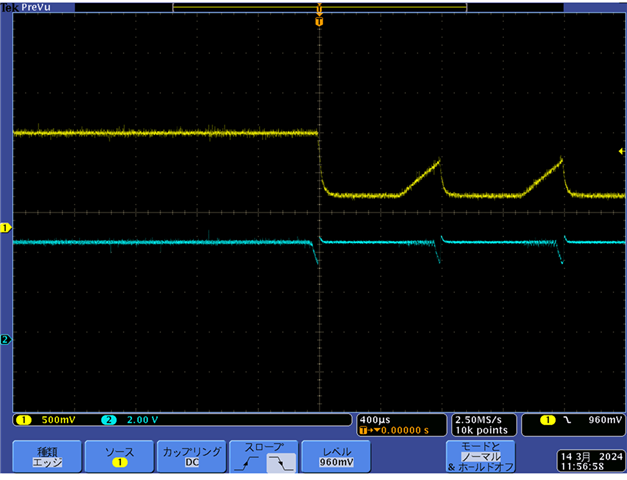

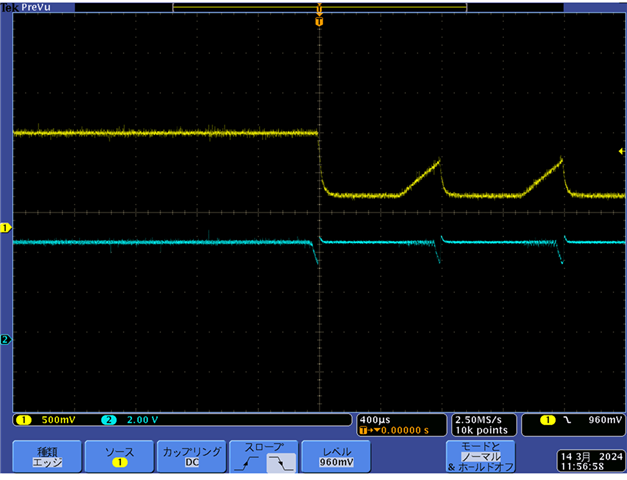

在以下波形中、Ch1是 VOUT、Ch2是 VREG。

下面随附了原理图。

e2e.ti.com/.../6406.Circuit.pdf

此致、

西井市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

当负载器件为使能时、VREG 下降并且 VOUT (1.2V)停止。 在大约6uS 之后、VOUT 上升并再次停止。

由于 VREG 引脚低于3.95V 的阈值、这似乎为 VOUT (1.2V)停止。 然而、VDD 引脚(4.5V 至25V)和 EN 引脚(0.6V)在一段时间内不会低于阈值。

你知道这是什么原因吗?

在以下波形中、Ch1是 VOUT、Ch2是 VREG。

下面随附了原理图。

e2e.ti.com/.../6406.Circuit.pdf

此致、

西井市

我在原理图中看不到可能导致 VREG 压降的任何内容、但 VREG 确实具有内部电流限制、如果负载过大、该限制将会压降。

1.0μF 旁路电容上80μs 中 VREG 的1.2V 下降由15mA 过量负载组成。

如果您在 VREG 下降时的最后一个80μs 期间放大开关节点、开关频率是多少?

连接到1.2V 输出的某器件可能打开并在超过0.6V 时消耗电流、并且转换器会显著提高开关频率以继续升高 VOUT、 并且较高开关频率下的栅极驱动电流超出 VREG LDO 的电流限制。

您能否提供同时在引脚上测量的 VDD 引脚电压的示波器图像?

尊敬的 Peter-San:

感谢您的支持。

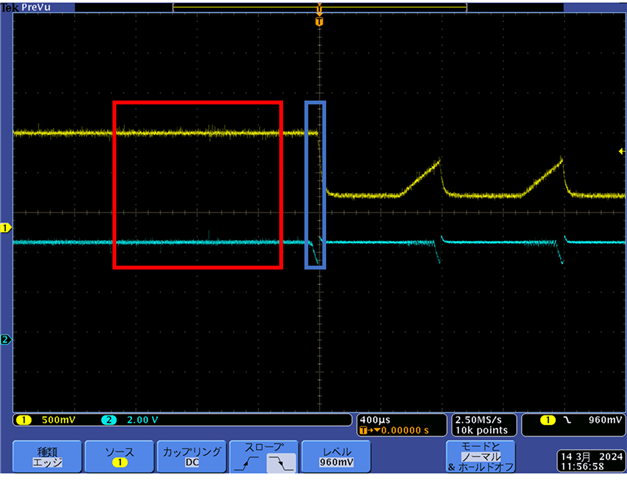

1)测量了红色框中的开关节点电压和 VDD 端子电压。 测量点是否正确? 您是指蓝色框中的测量值吗?

开关频率为500kHz。

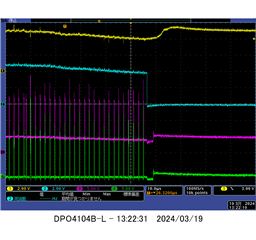

■Ch1是 VOUT、Ch2是 VREG

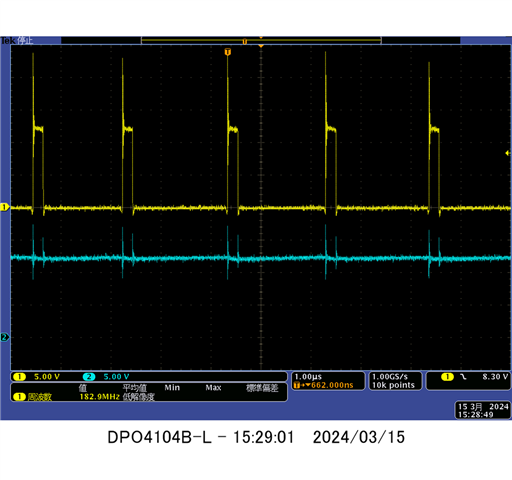

■通道1是 VSW、通道2是 VDD

2)当开关频率从500kHz 变为970kHz 时,启动电压(正常为500kHz)也会下降。 开关频率增大时、电压降是否增大?

此致、

西井市

1)测量了红框中的开关节点电压和 VDD 端子电压。 测量点是否正确? 是否指蓝色框中的测量?

抱歉我的指示不清楚。 是的、我是指在 VOUT 掉电时的蓝色帧期间。 如果您可以将 VOUT 下降沿设置为0.8V 作为触发点、并设置为5μs /除法的时间刻度、这应该会让我们对正在发生的情况有一些了解。

在您提供的 VDD 和 SW 图形中、我们可以看到负载电流正在增加。 如果仔细观察显示的最后2个周期、您可以看到开关节点顶部的斜率在增加、在每个周期下降更多。 此外、振铃减少后开关节点上的初始电压。 高侧 FET 上的压降正在增加、MOSFET 的输入电压也可能会降低。

2)开关频率从500kHz 变为970kHz 时,启动电压(通常为500kHz)也会下降。 开关频率增大时电压降是否增大?

更高的开关频率将增加 VREG 上的负载、因为更频繁地导通和关断 MOSFET 将需要更多电流。

MOSFET 驱动器本质上需要一定量的电荷(Q)才能在每个周期中导通。 这称为 MOSFET 的栅极电荷、当我们关断 MOSFET 时、它将丢失(放电)。 我们开启 MOSFET 的频率越高(开关频率越高)、需要的每秒电荷(即电流)就越多。

遗憾的是、根据原理图、我仍未看到任何会导致 VREG 放电和关断的东西。 开关频率未意外上升、原理图仅显示 VREG 上的 PGOOD 负载、而内部栅极驱动器除外。 当显示一些纹波时、VDD 仍保持高电平、应保持 VREG LDO 运行。

虽然3us 长 SW 低电平周期表明330nH 电感的负载电流为15-18A、但我们没有看到 VDD 或 SW 上的明显下降导致 VOUT 关断和 VREG 压降。

由于 PG 是唯一加载 VREG 的另一件设备,在最后几个开关周期内,是否可以通过在 VREG 下降时触发来获得显示 VREG、PG 和 VBST 的波形? 我想知道 R14的电阻值是否错误、PGOOD 触发器是否会使 VREG 放电、或者 R1或 R2的值是否错误且

尊敬的 Peter-San:

感谢您检查波形。 我明白、从波形中找不到原因。

我得到了一个新的波形。 您能从该波形中看出什么吗?

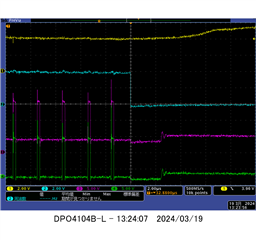

图1 1CH:Vreg、2ch:VPGOOD、3CH:VBST、4ch:VSW

图2 1通道:Vreg、2通道:VPGOOD、3通道:VBST、4通道:VSW (放大视图)

由于 PG 是加载 VREG 的唯一一件事,在最后几个开关周期内,在通过触发 VREG 下降来关闭 VREG 之前,是否能够获得显示 VREG、PG 和 VBST 的波形? 我想知道 R14的电阻值是否错误、PGOOD 触发器是否正在使 VREG 放电、或者 R1或 R2的值是否错误并 [/报价]最后一句以"和"结尾,是否有延续? 要求客户测量 R1、R2和 R14的实际电阻值是否正确?

此致、

西井市

Nichie、

您提供的波形没有显示问题与 R14和从 PGOOD 加载 VREG 相关的证据、我们看到 VREG 在 PGOOD 置为低电平之前放电。

您的最新波形显示、1μF 上的电容在30μs 上的 VREG 下降大约1V、超过33mA 的过度负载、这与 VREG 关闭是一致的。

您说 EN 不会降到0.6V 以下、您可以共享 EN 和 Vreg? 虽然 EN 上的0.6V 输入确保了不可禁用状态、但是实际阈值在1.0-1.2V 范围内会稍高一些。 EN 可能会下降并关闭 VREG LDO、然后通过 MOSFET 开关将其放电、直到触发 VREG UVLO 关闭和重新启动。

尊敬的 Peter-San:

感谢您检查波形。 我知道 R14或 PGOOD 没有问题。

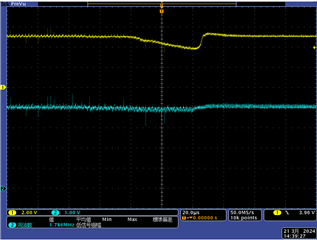

我还测量了 VREG 和 EN 波形。 请确认。

■1通道:Vreg、2ch:EN

有关其他信息、客户已确定以下电阻值:

1) 1) R1和 R2的电阻值分别为0.9 Ω 至1.2 Ω。

2) 2) 在发生问题的基板上的 VBST 引脚(4引脚)和 GNDpin 引脚之间测量电阻。 已知良好的基板的电阻为40M Ω 或更高(测试仪无法测量)。 有问题的基板具有14M Ω 至16.5 M Ω 的电阻。 我们测量了3个正常基板和2个有问题的基板。

这有什么用吗?

此致、

西井市

非常感谢你的评分

我还测量了 VREG 和 EN 波形。 请确认.

EN 显示在4V 左右、并且始终没有下降到足以触发 VREG 的关断、因此我认为这不是问题所在。

2) 电阻是在发生问题的基板上的 VBST 引脚(4引脚)和 GNDpin 引脚之间测量的。 已知良好的基板的电阻为40M Ω 或更高(测试仪无法测量)。 有问题的基板具有14M Ω 至16.5 M Ω 的电阻。 我们测量了3个正常基板和2个有问题的基板。[/报价]14兆欧姆的引导电阻不应足以感应 VREG 放电所需的更高负载电流、正如我们在这些波形中看到的那样、 但这可能表明 BOOT 引脚已损坏、当 BOOT 引脚在高侧开关期间高于 VIN 时、会引发其他问题。

您是否可以用有问题的部件替换"已知良好"的部件、并确定问题是出在部件还是主板? 可能需要为 FA 返回零件。

这些器件是从 TI.com 还是通过经销商购买的?

尊敬的 Peter-San:

我正在与客户核实部件的更换和来源。

时启动引脚高于 VIN

您能告诉我这种现象的模式和原因吗?

此致、

西井市

在运行期间、BOOT 引脚通常上升到 VIN 引脚以上。 当高侧 FET 导通时、SW 电压由内部高侧 MOSFET 拉至 VIN。 从 SW 到 BOOT 的电容器保持 BOOT 和 SW 引脚之间的电压、导致 BOOT 引脚上升到 VIN 以上。 这允许高侧驱动器的驱动器电路以 MOSFET 源为基准、MOSFET 源连接到 SW、并在 SW 上拉至 VIN 时继续为驱动器供电。

当高侧 MOSFET 关断且低侧导通时、驱动 SW 至 GND、自举电容器通过从 VREG 到 BOOT 的内部二极管从 VREG 重新充电。

通常、BOOT 上的泄漏电流很低、即使 BOOT 比 VIN 高6V 时也是如此、而 VREG 只需要在 BOOT 提供 MOSFET 开关所需的少量电荷的情况下提供 BOOT、每个开关周期几十纳库仑、 但是、如果在将 BOOT 拉至高电平时它上面存在额外的泄漏、例如可能导致引导器件损坏、则 VREG 还需要提供该额外的电流。

由于 VREG 的额定电压仅为30mA 提供电流、因此由于 BOOT 电路损坏或泄漏而产生的额外负载可能会导致 VREG 放电。

是的、应分析器件。 由于该器件是通过经销商购买的、因此客户应根据 TI 的故障分析材料政策联系经销商。

https://www.ti.com/support-quality/additional-information/customer-returns.html