您好!

我们使用的是 TPS3897P、其中 tpd (r)设置为通孔电容为5s。

当器件上电时、我们可以 看到在 Vcc 之前加电、然后使能在 VCC 之后大约200ms 变为高电平。

由于 ENABLE 是检测到的并且 VCC 已经很高、因此我们"认为"输出会立即变为高电平(TDP = 200ns)、但我们看到 SENSE_OUT 在上升至高电平之前的5秒内保持低电平。

是否在上电时预计会发生这种情况?

谢谢。

格伦

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们使用的是 TPS3897P、其中 tpd (r)设置为通孔电容为5s。

当器件上电时、我们可以 看到在 Vcc 之前加电、然后使能在 VCC 之后大约200ms 变为高电平。

由于 ENABLE 是检测到的并且 VCC 已经很高、因此我们"认为"输出会立即变为高电平(TDP = 200ns)、但我们看到 SENSE_OUT 在上升至高电平之前的5秒内保持低电平。

是否在上电时预计会发生这种情况?

谢谢。

格伦

你好、Joshua、

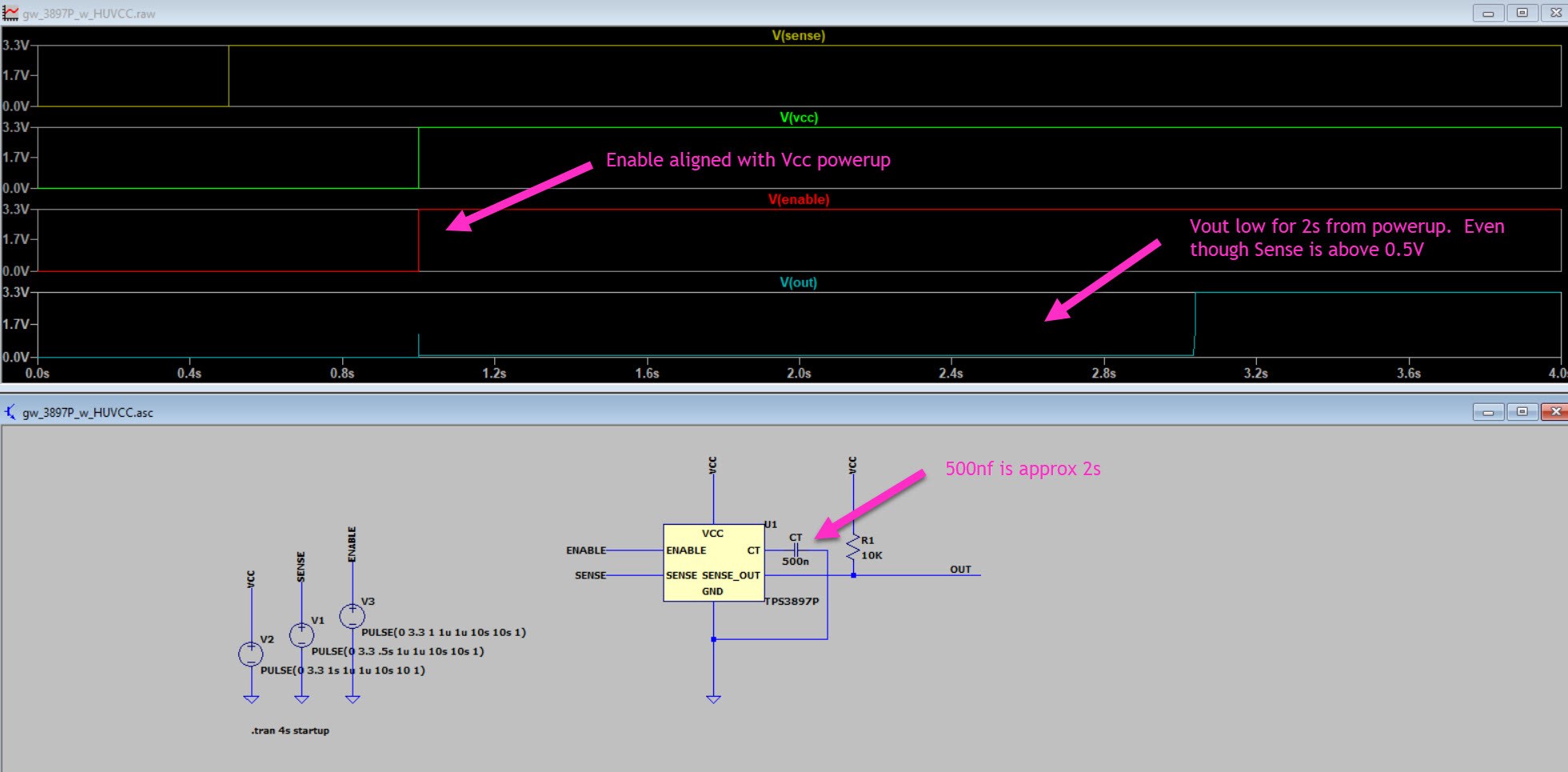

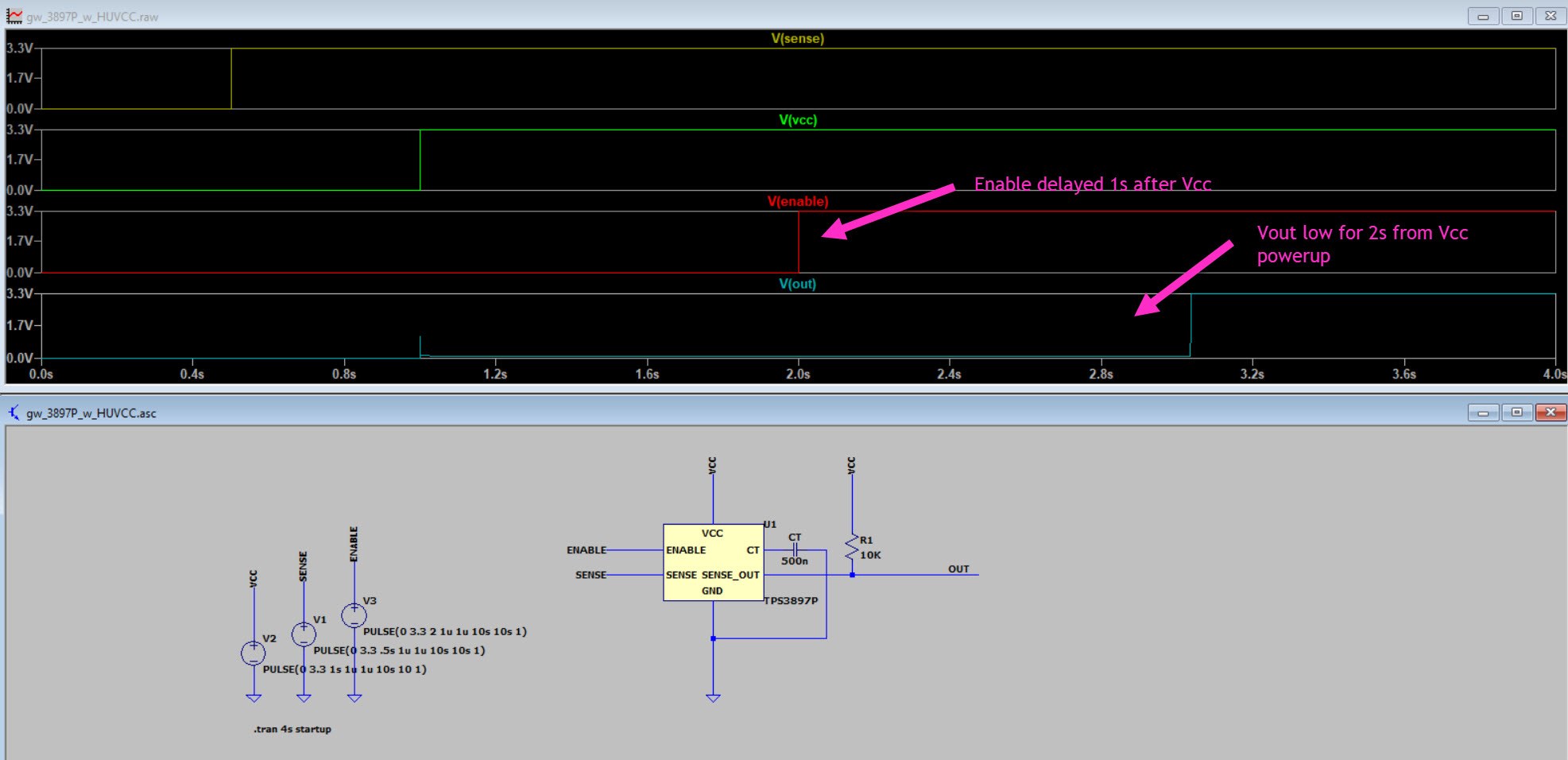

我整理了一个 SPICE 仿真来说明我们看到的情况。

在原理图中、我对 CT 使用了500nF、这相当于从 SENSE 上升到 SENSE_OUT 上升大约2s。

在全部3种情况下、SENSE 在 VCC 之前0.5s 处于高电平。

image1 -在 VCC 中启用

图像2 -在 VCC 后启用延迟1s

图像3 -在 VCC 后启用延迟2.5s