主题中讨论的其他器件: CSD19534KCS

e2e.ti.com/.../5241.TL494-BOOST-CONVERTER.pdf

上面是使用设计的 TL494的升压转换器的电路图。

1、业务问题

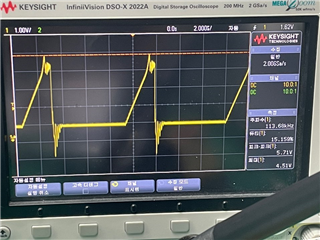

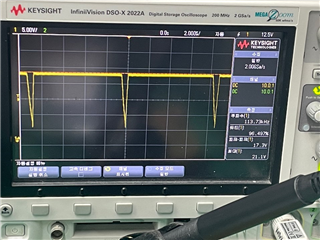

1.1施加电源时、MOSFET 受损、S 和 D 短路、电源 CC 工作

1.2与 SMD 型 NVMFS5H663NL MOSFET 相同的现象

2、判断元件的规格没有缺失,电路是否有问题?

3、电感 L1是用 IDC 30A 构建的,68uH,R6,R18 使用 GMR320HJAAFD5L00的电流感应电阻,F1 到 F5使用 NFM41PC155B1H3 EMI 滤波器。

4. 使用 TL494设计高功率、高效率的升压转换器(circuitdigest.com) 我参考了链接。