主题中讨论的其他器件: LM25149-Q1

您好!

我已经设计了一个使用 LM25148的电路板、以达到5V 输出@ 8A、以及15V 输入。

我已经使用数据表和 WebEnch 创建了设计。

我将使用电子负载测试设计。 它可以在 Vout = 5.02V 时达到3.0A。

在3.1A 时、PGOOD 变为低电平、Vout 降至4.33V。 VOUT 保持在4.33V 至5A。 我可以在 Vout=3V 的情况下达到11A。

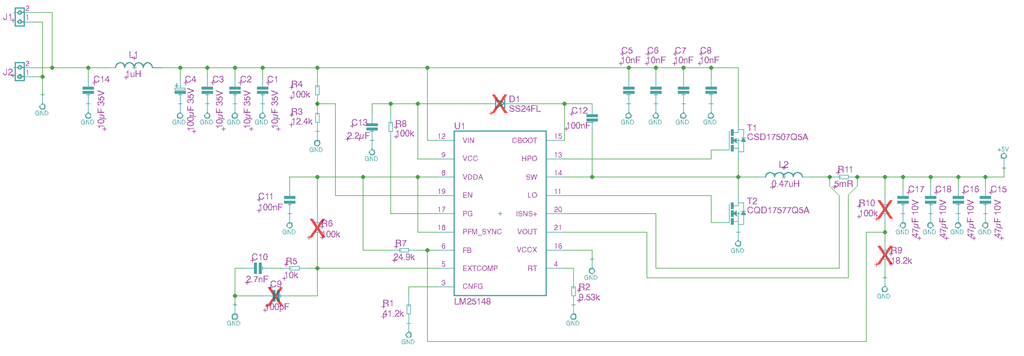

原理图

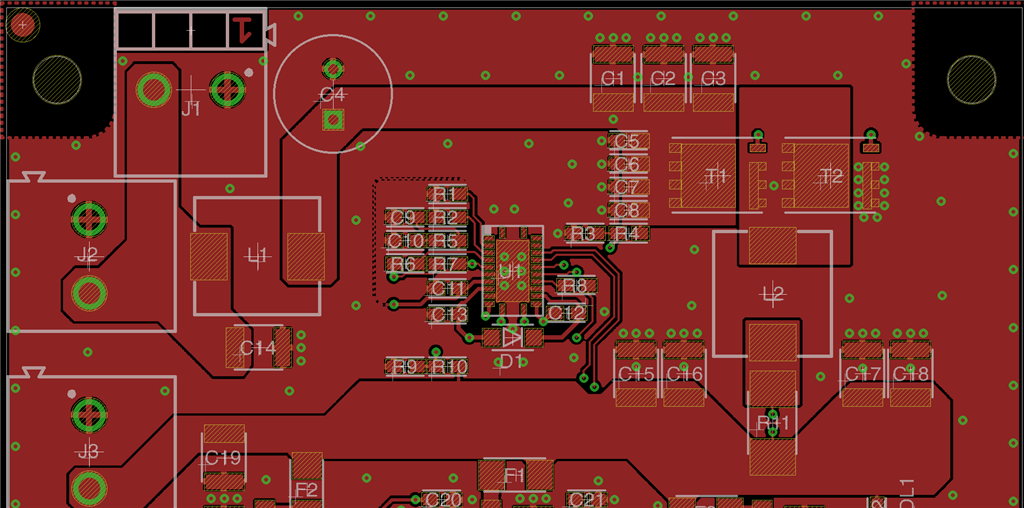

顶层布局

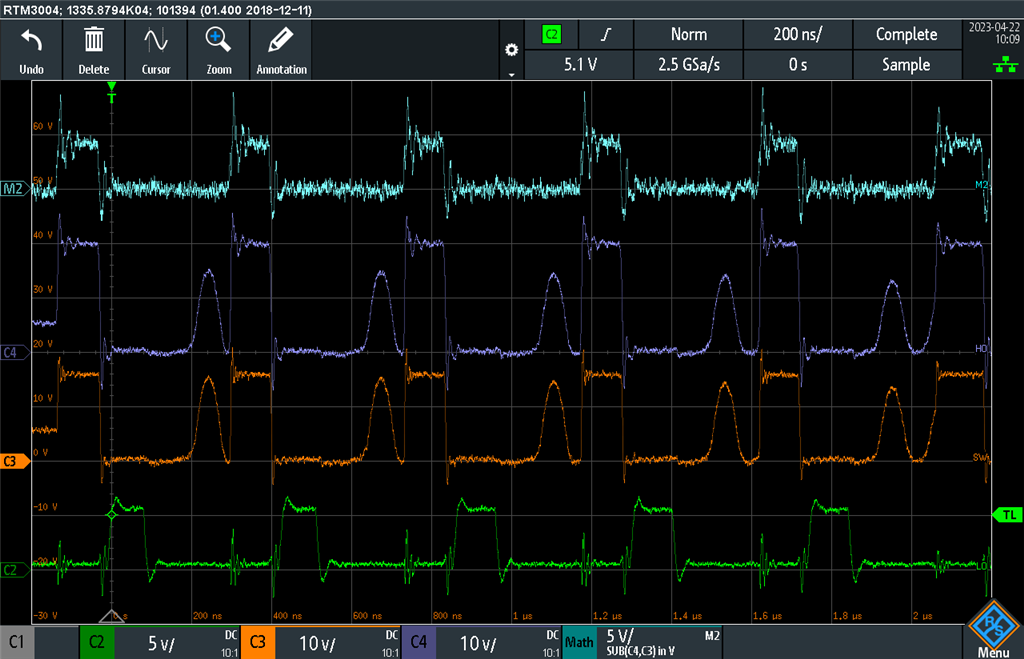

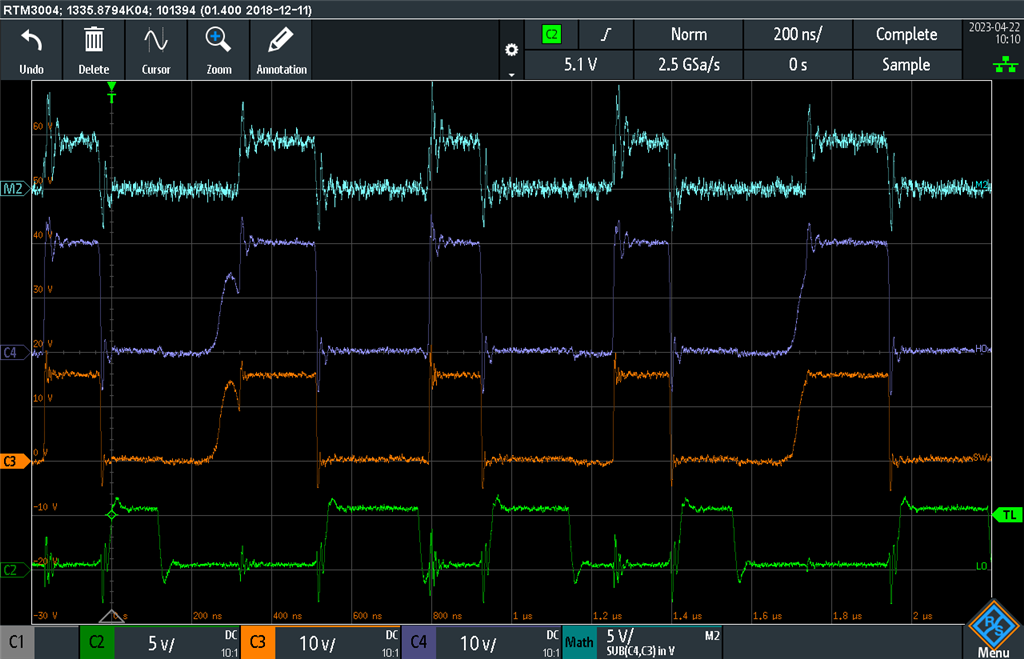

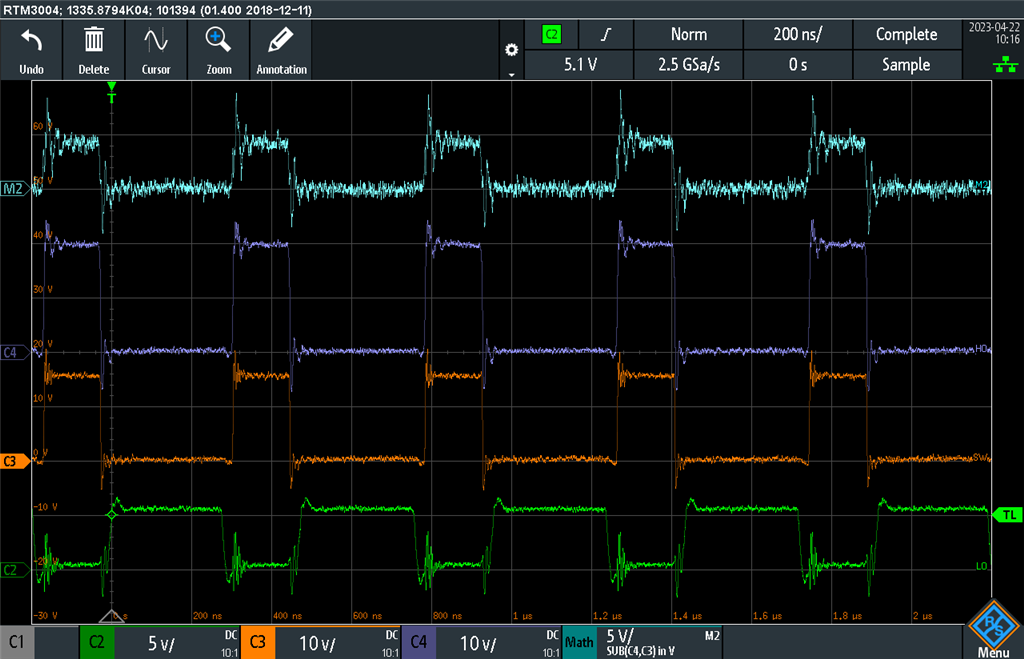

无负载:C2->LO;C3->SW;C4->HO; Math -> HO Minus SW

2A 负载。 输出电压= 5.02V

4A 负载、Vout 降至4.33V

有任何想法或线索吗?

感谢你的帮助。