您好

我使用的是 UCD3138CC64EVM-030A。

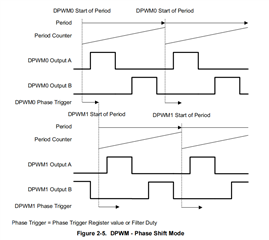

我希望 PWM 在相移模式下运行。 首先,我想通过一个简单的实验来实现它,但我发现了一些问题。

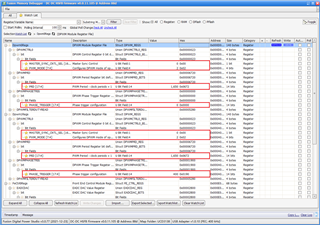

1. MASTER_SYNC_CNTL_SEL 位设置为0、主器件 SYNC 由相位触发器寄存器控制。

2. DPWM1的 PHASE_TRIGGER 位设置为400、DPWM0为0。

3. DPWM_MODE 位设置为2,多输出模式。

但在示波器上、DPWM0A 与 DPWM1A 完全一致、没有相位差。

那么、 我想问我的配置是否有什么问题?

此致、

Jie